2LL M.2 Module - Datasheet

Copyright 2025 © Embedded Artists AB

**Document status: Preliminary**

# 2LL M.2 Module Datasheet (EAR00500 / EAR00501)

- Wi-Fi 6, 802.11 a/b/g/n/ac/ax SISO HE20/MCS9

- Bluetooth 5.4 LE

- IEEE802.15.4

- SDIO 3.0 or USB2.0 interface

- Chipset: NXP IW610G

Get Up-and-Running Quickly and Start Developing Your Application on Day 1!

#### **Embedded Artists AB**

Rundelsgatan 14 211 36 Malmö Sweden

https://www.EmbeddedArtists.com

#### Copyright 2025 © Embedded Artists AB. All rights reserved.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Embedded Artists AB.

#### Disclaimer

Embedded Artists AB makes no representation or warranties with respect to the contents hereof and specifically disclaim any implied warranties or merchantability or fitness for any particular purpose. The information has been carefully checked and is believed to be accurate, however, no responsibility is assumed for inaccuracies.

Information in this publication is subject to change without notice and does not represent a commitment on the part of Embedded Artists AB.

#### Feedback

We appreciate any feedback you may have for improvements to this document.

#### Trademarks

All brand and product names mentioned herein are trademarks, services marks, registered trademarks, or registered service marks of their respective owners and should be treated as such.

# **Table of Contents**

| 1    | Document Information                                         | 4  |

|------|--------------------------------------------------------------|----|

| 1.1  | Revision History                                             | 4  |

| 2    | Introduction                                                 | 5  |

| 2.1  | Benefits of Using an M.2 Module to get Wireless Connectivity | 5  |

| 2.2  | More M.2 Related Information                                 | 5  |

| 2.3  | ESD Precaution and Handling                                  | 6  |

| 2.4  | Product Compliance                                           | 6  |

| 3    | Specification                                                | 7  |

| 3.1  | Power Up Sequence                                            | 8  |

| 3.2  | External Sleep Clock                                         | 8  |

| 3.3  | Mechanical Dimensions                                        | 9  |

| 3.4  | M.2 Pinning                                                  | 11 |

| 3.5  | On-board I2C GPIO Expander                                   | 15 |

| 3.6  | Block Diagram                                                | 16 |

| 3.7  | IEEE802.15.4 Interface                                       | 16 |

| 3.8  | SDIO Interface                                               | 17 |

| 3.9  | Wi-Fi / Bluetooth Interface Control                          | 18 |

| 3.10 | Test Points and Expansion Header                             | 19 |

| 3.11 | Current Consumption Measurements                             | 20 |

| 4    | Antenna                                                      | 21 |

| 4.1  | Reference Certified External Antenna                         | 21 |

| 4.2  | Antenna Connector                                            | 21 |

| 4.3  | Mounting and Clearance for On-board Antenna                  | 22 |

| 4.4  | Overriding on-board PCB Trace Antenna                        | 23 |

| 4.5  | On-board PCB Trace Antenna Performance                       | 24 |

| 5    | Software and Support                                         | 27 |

| 5.1  | Software Driver                                              | 27 |

| 5.2  | Support                                                      | 27 |

| 6    | Regulatory                                                   | 28 |

| 6.1  | European Union Regulatory Compliance                         | 28 |

| 7    | Disclaimers                                                  | 29 |

| 7.1  | Definition of Document Status                                | 30 |

# **1** Document Information

This document applies to the following products.

| Product Name                         | Type Number         | Murata Module | Chipset    | Product Status     |

|--------------------------------------|---------------------|---------------|------------|--------------------|

| 2LL M.2 Module,<br>rev PA3 and later | EAR00500 / EAR00501 | LBES0ZZ2LL    | NXP IW610G | Initial Production |

This table below lists the product differences. All products are not stocked. Consult Embedded Artists for availability and lead time.

| Type Number | Product Name   | Antenna                                | Packaging                         |

|-------------|----------------|----------------------------------------|-----------------------------------|

| EAR00500    | 2LL M.2 Module | External antenna via<br>u.fl.connector | Individual packing for evaluation |

| EAR00501    | 2LL M.2 Module | External antenna via<br>u.fl.connector | Tray packing                      |

### 1.1 Revision History

| Revision | Date       | Description                                                              |  |

|----------|------------|--------------------------------------------------------------------------|--|

| PA1      | 2024-11-27 | First version.                                                           |  |

| PA2      | 2024-11-29 | Corrected antenna information.                                           |  |

| PA3      | 2025-02-06 | Removed Bluetooth Classic. Added information about current and TX power. |  |

# 2 Introduction

This document is a datasheet that specifies and describes the 2LL M.2 module mainly from a hardware point of view.

The main component in the design is Murata's 2LL module (full part number: LBES0ZZ2LL), which in turn is based on the NXP IW610G chipset, respectively. The 2LL module enables Wi-Fi and Bluetooth Low Energy (LE).

There are multiple application areas for the 2LL M.2 Module:

- Industrial and Buildings automation

- Asset management

- IoT applications

- Smart home: Voice assist device, smart printer, smart speaker, home automation gateway, and IP camera

- Retail/POS

- Healthcare and medical devices

- Smart city

- and many more...

#### 2.1 Benefits of Using an M.2 Module to get Wireless Connectivity

There are several benefits to using an *M.2 module* to add connectivity to an embedded design:

- Drop-in, certified solution!

- Modular and flexible approach to evaluate different Wi-Fi / BT solutions with different tradeoffs around performance, cost, power consumption, longevity, etc.

- Access to maintained software drivers (Linux and SDK) with responsive support from Murata.

- Supported by Embedded Artists' Developer's Kits for i.MX RT/8/9 development, including advanced debugging support on carrier boards

- Futureproofing the design easy to replace with a newer module in the future

- One component to buy, instead of 40+

- No RF expertise is required

- Developed in close collaboration with Murata

#### 2.2 More M.2 Related Information

For more information about the M.2 standard and Embedded Artists' adaptation, see: M.2 Primer For more general information about the M.2 standard, see: https://en.wikipedia.org/wiki/M.2 The official M.2 specification (PCI Express M.2 Specification) is available from: www.pcisig.com

### 2.3 ESD Precaution and Handling

Please note that the M.2 module come without any case/box and all components are exposed for finger touches – and therefore extra attention must be paid to ESD (electrostatic discharge) precaution, for example use of static-free workstation and grounding strap. Only qualified personnel shall handle the product.

Make it a habit always to first touch the mounting hole (which is grounded) for a few seconds with both hands before touching any other parts of the boards. That way, you will have the same potential as the board and therefore minimize the risk for

ESD.

In general, touch as little as possible on boards to minimize the risk of ESD damage. The only reasons to touch the board are when mounting/unmounting it on a carrier board.

Note that Embedded Artists does not replace modules that have been damaged by ESD.

#### 2.4 Product Compliance

Visit Embedded Artists' website at http://www.embeddedartists.com/product\_compliance for up-to-date information about product compliances such as CE, UKCA, RoHS2/3, Conflict Minerals, REACH, etc.

# 3 Specification

This chapter lists some of the more important characteristics of the M.2 module, but it is not a full specification of performance and timing. The main component in the design is Murata's 2LL module (full part number: LBES0ZZ2LL), which in turn is based around NXP's IW610G chipset.

For a detailed specification, see the LBES0ZZ2LL product page at Murata: https://www.murata.com/products/connectivitymodule/wi-fi-bluetooth/overview/lineup/type2ll For full specification, see Murata's 2LL Module (LBES0ZZ2LL) product page: url tbd

| Module / Chipset |                                                                                 |

|------------------|---------------------------------------------------------------------------------|

| Murata module    | LBES0ZZ2LL                                                                      |

| Chipset          | NXP IW610G                                                                      |

|                  |                                                                                 |

| Wi-Fi            |                                                                                 |

| Standards        | 802.11a/b/g/n/ac/ax 1x1 SISO HE20/MCS9, Wi-Fi 6                                 |

| Network          | uAP and STA dual mode                                                           |

| Frequency        | 2.4GHz and 5 GHz band                                                           |

| Data rates       | Up to 114.7 Mbps                                                                |

| Host interface   | SDIO 3.0, SDR12@25MHz, SDR25@50MHz, SDR50@100MHz,                               |

|                  | SDR104@208MHz, DDR50@50MHz, or                                                  |

|                  | USB2.0                                                                          |

| Bluetooth        |                                                                                 |

|                  |                                                                                 |

| Standards        | 5.4 LE, 2Mbps PHY                                                               |

| Power Class      | Class 1.5                                                                       |

| Host interface   | 4-wire UART@4MBaud                                                              |

| Audio interface  | PCM for audio                                                                   |

|                  |                                                                                 |

| IEEE802.15.4     |                                                                                 |

| Standards        | IEEE 802.15.4-2015 compliant MAC, supporting Matter over Thread in 2.4 GHz band |

| PA               | Integrated high power PA up to +15 dBm transmit power                           |

| Host interface | SPI@10MHz                                                         |

|----------------|-------------------------------------------------------------------|

|                |                                                                   |

|                |                                                                   |

|                | Note: the maximum SPI clock frequency is limited to 1MHz for Open |

|                | 1 2 1                                                             |

|                | thread implementations.                                           |

| Powering                                             |                                     |      |       |

|------------------------------------------------------|-------------------------------------|------|-------|

| Operating conditions on supply voltage to M.2 module | Min                                 | Тур  | Max   |

|                                                      | 0.0V minimum<br>3.15V operating and | 3.3V | 3.46V |

|                                                                 |                         | RF specification                                                                                   |           |

|-----------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------|-----------|

| Absolute maximum rating on suppl                                | y voltage to M.2 module | Min                                                                                                | Мах       |

| Note: Do not exceed minimum o<br>Module will be permanently dam | 0.0V                    | 3.63V                                                                                              |           |

| Peak current                                                    | About 750 mA max        | The power supply must to<br>this peak current, which the<br>happens during the started<br>process. | typically |

| Receive mode current (WLAN)                                     | 95 mA typical max       | Note that current consum widely between different modes.                                           | •         |

| Transmit mode current (WLAN)                                    | 570 mA typical max      | Note that current consum widely between different modes.                                           |           |

| Environmental Specification                   |                            |

|-----------------------------------------------|----------------------------|

| Operational Temperature                       | -40 to +85 degrees Celsius |

| Storage Temperature                           | -40 to +85 degrees Celsius |

| Relative Humidity (RH), operating and storage | 10 - 90% non-condensing    |

### 3.1 Power Up Sequence

The supply voltage shall not rise (10 - 90%) faster than 40 microseconds and not slower than 100 milliseconds.

Chipset signals PD\_N (M.2 signal W\_DISABLE1#) must be held low for at least 2 milliseconds after supply voltage has reached specification level before pulled high.

### 3.2 External Sleep Clock

The sleep clock signals can be applied to a powered and unpowered M.2 module.

| Clock Specification |                                                                |  |  |  |

|---------------------|----------------------------------------------------------------|--|--|--|

| Frequency           | 32.768 kHz                                                     |  |  |  |

| Frequency accuracy  | ±250 ppm including initial tolerance, aging, temperature, etc. |  |  |  |

| Duty cycle          | 30 - 70%                                                       |  |  |  |

| Voltage level       | 3.3V logic, according to M.2 standard                          |  |  |  |

#### 3.3 Mechanical Dimensions

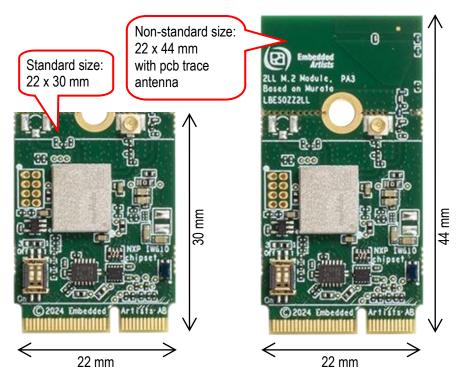

The M.2 module is of type: 2230-D5-E according to the M.2 nomenclature. This means width 22 mm, length 30mm (without trace antenna), top and bottom side component height 1.5 mm and key-E connector. The table below lists the different dimensions and weight.

| M.2 Module Dimension                    | Value (±0.15 mm) | Unit |

|-----------------------------------------|------------------|------|

| Width                                   | 22               | mm   |

| Height, without pcb trace antenna       | 30               | mm   |

| PCB thickness                           | 0.8              | mm   |

| Maximum component height on top side    | 1.5              | mm   |

| Maximum component height on bottom side | 1.5              | mm   |

| Ground hole diameter                    | 3.5              | mm   |

| Plating around ground hole, diameter    | 5.5              | mm   |

| Module weight                           | 1.5 ±0.5 gram    | gram |

Embedded Artists has added a non-standard feature to the 2230 M.2 modules designed together with Murata, NXP and Infineon (former Cypress). The pictures below illustrate how the standard module size has been extended by 14 mm in the length direction to include a pcb trace antenna.

Figure 1 - M.2 Module with, and without, PCB Trace Antenna

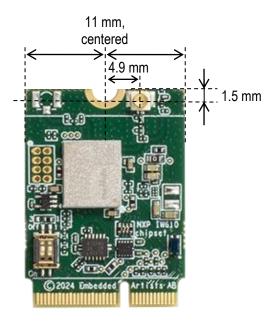

Figure 2 – M.2 Module Antenna Connector Measurements

#### 3.4 M.2 Pinning

This section presents the pinning used for the M.2 module. It is essentially M.2 Key-E compliant with enhancements to support additional debug signals. The pin assignment for specific control has been jointly defined by Embedded Artists, Murata, NXP and Infineon.

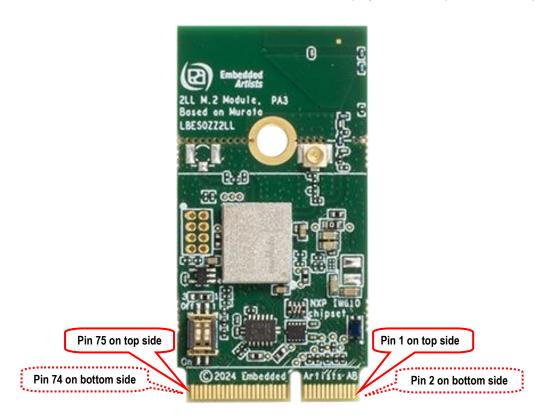

The picture below illustrates the edge pin numbering. It starts on the right edge and alternates between the top and bottom side. The removed pads in the keying notch count (but are obviously non-existing).

Figure 3 – M.2 Module Pin Numbering

The Wi-Fi interface uses the SDIO interface as default, but it is possible to configure the module to use the USB interface instead, see section 0for details. If Wi-Fi uses the SDIO interface, the Bluetooth interface uses the UART interface for control and PCM interface for audio. If Wi-Fi uses the USB interface, the Bluetooth interface also uses the USB interface.

The table below lists the pin usage for the 2LL M.2 modules. The column "When is signal needed" signals different categories:

- Always: These signals shall always be connected.

- Wi-Fi SDIO: These signals shall always be connected when the Wi-Fi SDIO interface is used.

- USB: These signals shall always be connected when the USB interface is used.

- Bluetooth UART (audio): These signals shall always be connected when the Bluetooth UART interface is used. If the USB interface is used, Bluetooth will also use the USB interface.

- IEEE802.15.4: These SPI signals shall always be connected when the IEEE802.15.4 interface is used.

- Optional: These signals are optional to connect.

| Pin # | Side<br>of pcb | M.2 Name   | Voltage Level and<br>Signal Direction | When is<br>signal needed | Note                                                                                                              |

|-------|----------------|------------|---------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------|

| 1     | Тор            | GND        | GND                                   | Always                   | Connect to ground                                                                                                 |

| 2     | Bottom         | 3.3 V      |                                       | Always                   | Power supply input. Connect to stable, low-noise 3.3V supply.                                                     |

| 3     | Тор            | USB_D+     |                                       | USB                      | For USB interface: USB_DP.                                                                                        |

|       |                |            |                                       |                          | Connected to 2LL module, signal USB_DP, pad 77                                                                    |

| 4     | Bottom         | 3.3 V      |                                       | Always                   | Power supply input. Connect to stable, low-noise 3.3V supply.                                                     |

| 5     | Тор            | USB_D-     |                                       | USB                      | For USB interface: USB_DM.                                                                                        |

|       |                |            |                                       |                          | Connected to 2LL module, signal USB_DM, pad 78                                                                    |

| 6     | Bottom         | LED_1#     |                                       |                          | Not connected.                                                                                                    |

| 7     | Тор            | GND        | GND                                   | Always                   | Connect to ground.                                                                                                |

| 8     | Bottom         | PCM_CLK    |                                       |                          | Not connected.                                                                                                    |

| 9     | Тор            | SDIO CLK   | 1.8V Input to M.2                     | Wi-Fi SDIO               | For Wi-Fi SDIO interface: SDIO_CLK                                                                                |

|       |                |            |                                       |                          | Connected to 2LL module, signal SDIO_CLK, pad 44                                                                  |

| 10    | Bottom         | PCM_SYNC   |                                       |                          | Not connected.                                                                                                    |

| 11    | Тор            | SDIO CMD   | 1.8V I/O                              | Wi-Fi SDIO               | For Wi-Fi SDIO interface: SDIO_CMD                                                                                |

|       |                |            |                                       |                          | Connected to 2LL module, signal SDIO_CMD, pad 42                                                                  |

|       |                |            |                                       |                          | Note: Require an external 10-100K ohm pullup                                                                      |

| 12    | Bottom         | PCM_OUT    |                                       |                          | Not connected.                                                                                                    |

| 13    | Тор            | SDIO DATA0 | 1.8V I/O                              | Wi-Fi SDIO               | For Wi-Fi SDIO interface: SDIO_D0                                                                                 |

|       |                |            |                                       |                          | Connected to 2LL module, signal SDIO_DATA_0, pad 48                                                               |

|       |                |            |                                       |                          | Note: Require an external 10-100K ohm pullup                                                                      |

| 14    | Bottom         | PCM_IN     |                                       |                          | Not connected.                                                                                                    |

| 15    | Тор            | SDIO DATA1 | 1.8V I/O                              | Wi-Fi SDIO               | For Wi-Fi SDIO interface: SDIO_D1                                                                                 |

|       |                |            |                                       |                          | Connected to 2LL module, signal SDIO_DATA_1, pad 45                                                               |

|       |                |            |                                       |                          | Note: Require an external 10-100K ohm pullup                                                                      |

| 16    | Bottom         | LED_2#     |                                       |                          | Not connected.                                                                                                    |

| 17    | Тор            | SDIO DATA2 | 1.8V I/O                              | Wi-Fi SDIO               | For Wi-Fi SDIO interface: SDIO_D2                                                                                 |

|       |                |            |                                       |                          | Connected to 2LL module, signal SDIO_DATA_2, pad 47                                                               |

|       |                |            |                                       |                          | Note: Require an external 10-100K ohm pullup                                                                      |

| 18    | Bottom         | GND        |                                       | Always                   | Connect to ground.                                                                                                |

| 19    | Тор            | SDIO DATA3 | 1.8V I/O                              | Wi-Fi SDIO               | For Wi-Fi SDIO interface: SDIO_D3                                                                                 |

|       |                |            |                                       |                          | Connected to 2LL module, signal SDIO_DATA_3, pad 46                                                               |

|       |                |            |                                       |                          | Note: Require an external 10-100K ohm pullup                                                                      |

| 20    | Bottom         | UART WAKE# | 3.3V push-pull output                 | Bluetooth UART           | For Bluetooth UART interface: NB_WAKE_OUT                                                                         |

|       |                |            | from M.2                              |                          | This is a wake signal for the Bluetooth/802.15.4 interfaces from the device (Wi-Fi/BT chipset) to the host (CPU). |

|       |                |            |                                       |                          | Connected to 2LL module, via buffer, signal NB_WAKE_OUT, pad 76.                                                  |

|       |                |            |                                       |                          | This pin can also be JTAG_TDO output.                                                                             |

| 21    | Тор            | SDIO WAKE# | 1.8V OD output from                   | Wi-Fi SDIO               | For Wi-Fi SDIO interface WL_WAKE_OUT                                                                              |

|       |                |            | M.2                                   |                          | This is a wake signal for the Wi-Fi interface from the device (Wi-Fi/BT chipset) to the host (CPU).               |

|       |                |            |                                       |                          | Connected to 2LL module, via buffer, signal WL_WAKE_OUT, pad 73                                                   |

|    |          |                   |                      |                 | This pin can also be JTAG_TDI input.                                                                                        |

|----|----------|-------------------|----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

|    |          |                   |                      |                 | Note: Require an external 10K pullup resistor to 1.8V                                                                       |

| 22 | Bottom   | UART TXD          | 1.8V output from M.2 | Bluetooth UART  | For Bluetooth UART interface: UART_SOUT/UART_TXD                                                                            |

|    |          |                   |                      |                 | Connected to 2LL module, signal UART_SOUT, pad 49                                                                           |

| 23 | Тор      | SDIO RESET#       | 1.8V input to M.2    | Optional        | Independent reset signal for Wi-Fi functionality.                                                                           |

|    |          |                   |                      |                 | Connected to 2LL module, signal IND_RST_WL, pad 63.                                                                         |

|    |          |                   |                      |                 | SDIO RESET#: High = Wi-Fi part of module enabled/internally<br>powered, Low = Wi-Fi disabled/powered down.                  |

| 24 | Key, non | existing          |                      |                 |                                                                                                                             |

| 25 | Key, non | existing          |                      |                 |                                                                                                                             |

| 26 | Key, non | existing          |                      |                 |                                                                                                                             |

| 27 | Key, non | existing          |                      |                 |                                                                                                                             |

| 28 | Key, non | existing          |                      |                 |                                                                                                                             |

| 29 | Key, non | existing          |                      |                 |                                                                                                                             |

| 30 | Key, non | existing          |                      |                 |                                                                                                                             |

| 31 | Key, non | existing          |                      |                 |                                                                                                                             |

| 32 | Bottom   | UART_RXD          | 1.8V input to M.2    | Bluetooth UART  | For Bluetooth UART interface: UART_SIN/UART_RXD                                                                             |

|    |          |                   |                      |                 | Connected to 2LL module, signal UART_SIN pad 51                                                                             |

| 33 | Тор      | GND               |                      | Always          | Connect to ground.                                                                                                          |

| 34 | Bottom   | UART_RTS          | 1.8V output from M.2 | Bluetooth UART  | For Bluetooth UART interface: UART_RTSn                                                                                     |

|    |          | -                 | ·                    |                 | Connected to 2LL module, signal UART_RTSn, pad 52                                                                           |

| 35 | Тор      | PERp0             |                      |                 | Not connected.                                                                                                              |

| 36 | Bottom   | UART_CTS          | 1.8V input to M.2    | Bluetooth UART  | For Bluetooth UART interface: UART_CTSn                                                                                     |

| 00 | Bottom   | 0/11/1_010        |                      | Didotocal chara | Connected to 2LL module, signal UART_CTSn, pad 50                                                                           |

| 37 | Тор      | PERn0             |                      |                 | Not connected.                                                                                                              |

| 38 | Bottom   | VENDOR            | 1.8V input to M.2    | IEEE802.15.4    | SPI MOSI, the SPI data signal (from host to M.2) for the                                                                    |

| 50 | DOLIOIT  | DEFINED           |                      | ILLL002.13.4    | IEEE802.15.4/SPI interface.                                                                                                 |

|    |          |                   |                      |                 | Connected to 2LL module, via buffer, signal<br>SPI_RXD/PCM_SYNC, pin 6.                                                     |

|    |          |                   |                      |                 | The buffer is only enabled if bit 0 of the on-board I2C GPIO expander is set to 1.                                          |

| 39 | Тор      | GND               |                      | Always          | Connect to ground.                                                                                                          |

| 40 | Bottom   | VENDOR            | 1.8V output from M.2 | IEEE802.15.4    | SPL_MISO, the SPI data signal (from M.2 to host) for the                                                                    |

|    |          | DEFINED           |                      |                 | IEEE802.15.4/SPI interface.                                                                                                 |

|    |          |                   |                      |                 | Connected to 2LL module, via buffer, signal SPI_TXD, pin 7.<br>The buffer is only enabled if bit 0 of the on-board I2C GPIO |

|    |          |                   |                      |                 | expander is set to 1.                                                                                                       |

| 41 | Тор      | PETp0             |                      |                 | Not connected.                                                                                                              |

| 42 | Bottom   | VENDOR<br>DEFINED | 1.8V input to M.2    | IEEE802.15.4    | SPI_SCK, the SPI clock signal (from host to M.2) for the<br>IEEE802.15.4/SPI interface.                                     |

|    |          |                   |                      |                 | Connected to 2LL module, via buffer, signal SPI_CLK, pin 8.                                                                 |

|    |          |                   |                      |                 | The buffer is only enabled if bit 0 of the on-board I2C GPIO expander is set to 1.                                          |

| 43 | Тор      | PETn0             |                      |                 | Not connected.                                                                                                              |

|    | Bottom   | COEX3             |                      |                 | Not connected.                                                                                                              |

| 44 | DOLLOITI | OOLAO             |                      |                 |                                                                                                                             |

| 46 | Bottom | COEX_TXD                 | 1.8V I/O            | Optional     | Connected to 2LL module, signal GPIO_2, pad 58.                                                                       |

|----|--------|--------------------------|---------------------|--------------|-----------------------------------------------------------------------------------------------------------------------|

|    |        |                          |                     |              | Note: Signal can be JTAG_TCK                                                                                          |

| 47 | Тор    | REFCLKp0                 |                     |              | Not connected.                                                                                                        |

| 48 | Bottom | COEX_RXD                 | 1.8V I/O            | Optional     | Connected to 2LL module, signal GPIO_3, pad 59.                                                                       |

|    |        |                          |                     |              | Note: Signal can be JTAG_TMS                                                                                          |

| 49 | Тор    | REFCLKn0                 |                     |              | Not connected.                                                                                                        |

| 50 | Bottom | SUSCLK                   |                     |              | Not connected.                                                                                                        |

| 51 | Тор    | GND                      |                     | Always       | Connect to ground.                                                                                                    |

| 52 | Bottom | PERST0#                  |                     |              | Not connected.                                                                                                        |

| 53 | Тор    | CLKREQ0#                 |                     |              | Not connected.                                                                                                        |

| 54 | Bottom | W_DISABLE2#              | 3.3V input to M.2   | Always       | Independent reset signal for Bluetooth/ IEEE802.15.4<br>functionality.                                                |

|    |        |                          |                     |              | Connected to 2LL module, via buffer, signal IND_RST_NB, pad 64.                                                       |

|    |        |                          |                     |              | W_DISABLE#2: High = Bluetooth part of module<br>enabled/internally powered, Low = Bluetooth disabled/powered<br>down. |

| 55 | Тор    | PEWAKE0#                 |                     |              | Not connected.                                                                                                        |

| 56 | Bottom | W_DISABLE1#              | 3.3V input to M.2   | Always       | Connected to 2LL module, via buffer, signal PD_N, pad 10.                                                             |

|    |        |                          |                     |              | W_DISABLE1#: High = The module is enabled/internally<br>powered, Low = The module is disabled/powered down .          |

| 57 | Тор    | GND                      |                     | Always       | Connect to ground.                                                                                                    |

| 58 | Bottom | I2C_SDA                  | 1.8V I/O            | IEEE802.15.4 | I2C data signal, connected to on-board GPIO expander, PCAL6408A.                                                      |

|    |        |                          |                     |              | The pin has a 10Kohm pullup resistor to an internal 1.8V.                                                             |

| 59 | Тор    | Reserved                 |                     |              | Not connected.                                                                                                        |

| 60 | Bottom | I2C_CLK                  | 1.8V input to M.2   | IEEE802.15.4 | I2C clock signal, connected to on-board GPIO expander, PCAL6408A.                                                     |

|    |        |                          |                     |              | The pin has a 10Kohm pullup resistor to an internal 1.8V.                                                             |

| 61 | Тор    | Reserved                 |                     |              | Not connected.                                                                                                        |

| 62 | Bottom | ALERT#                   | 1.8V OD output from | IEEE802.15.4 | SPI_INT, interrupt signal from the IEEE802.15.4/SPI interface.                                                        |

|    |        |                          | M.2                 |              | Connected to 2LL module, via an open-drain buffer, to signal SPI_INT, pin 5.                                          |

| 63 | Тор    | GND                      |                     | Always       | Connect to ground.                                                                                                    |

| 64 | Bottom | RESERVED                 | 1.8V input to M.2   | IEEE802.15.4 | SPI_SSEL, SPI select signal for the IEEE802.15.4/SPI interface.                                                       |

|    |        |                          |                     |              | Connected to 2LL module, via buffer, signal SPI_FRM, pin 4.                                                           |

|    |        |                          |                     |              | The buffer is only enabled if bit 0 of the on-board I2C GPIO expander is set to 1.                                    |

| 65 | Тор    | Reserved                 |                     |              | Not connected.                                                                                                        |

| 66 | Bottom | UIM_SWP                  |                     |              | Not connected.                                                                                                        |

| 67 | Тор    | Reserved                 |                     |              | Not connected.                                                                                                        |

| 68 | Bottom | UIM_POWER_<br>SNK        |                     |              | Not connected.                                                                                                        |

| 69 | Тор    | GND                      |                     | Always       | Connect to ground.                                                                                                    |

| 70 | Bottom | UIM_POWER_<br>SRC/GPIO_1 |                     |              | Not connected.                                                                                                        |

| 71 | Тор    | Reserved                 |                     |              | Not connected.                                                                                                        |

|    |        |                          |                     |              |                                                                                                                       |

| 72 | Bottom | 3.3 V    | Always | Power supply input. Connect to stable, low-noise 3.3V supply. |

|----|--------|----------|--------|---------------------------------------------------------------|

| 73 | Тор    | Reserved |        | Not connected.                                                |

| 74 | Bottom | 3.3 V    | Always | Power supply input. Connect to stable, low-noise 3.3V supply. |

| 75 | Тор    | GND      | Always | Connect to ground.                                            |

### 3.5 On-board I2C GPIO Expander

The IW610G chipsets need several control signals and there is a limited number of available pins in the M.2 standard. To create four output signals and one input signal, there is an on-board I2C GPIO expander, PCAL6408A. It can be accessed at I2C address 0x20 (7-bit address) or 0x40/0x41 (8-bit address).

The table below lists the usage of the four output signals and one input signal.

| Bit | Signal Name     | Direction | Usage / Connection                                                                                                                                                                                  |

|-----|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | SPI_ENABLE      | output    | 0 = The SPI interface of the IW610G chipset is not<br>connected to M.2 pins 38, 40, 42, and 64. The SPI<br>interface can however be accessed via the expansion<br>header, see section 0for details. |

|     |                 |           | 1= Connect SPI interface of IW610G chipset to M.2 pins 38, 40, 42 and 64.                                                                                                                           |

| 1   | IND_RST_15_4    | output    | Independent reset signal for IEEE802.15.4                                                                                                                                                           |

|     |                 |           | Connects to 2LL module, signal GPIO_11, pin 38                                                                                                                                                      |

| 2   | IND_WAKE_WLAN   | output    | Wi-Fi wakeup signal from host to IW610G chipset<br>WL_WAKE_IN                                                                                                                                       |

|     |                 |           | Connects to 2LL module, signal GPIO_16, pin 74                                                                                                                                                      |

| 3   | IND_WAKE_BT15_4 | output    | Bluetooth and IEEE802.15.4 wakeup signal from host to IW610G chipset.                                                                                                                               |

|     |                 |           | Connects to 2LL module, signal GPIO_17, pin 75.                                                                                                                                                     |

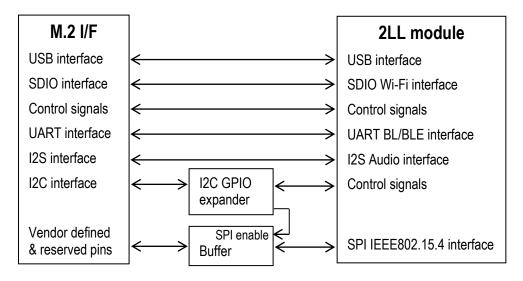

#### 3.6 Block Diagram

It can be difficult to understand the internal structure from just ready pin definitions. The block diagram below explains the 2LL M.2 internal structure with blocks instead. One of the I2C-GPIOs is used to control the buffer that enables/disables the SPI interface.

Figure 4 – 2LL M.2 Module Block Diagram

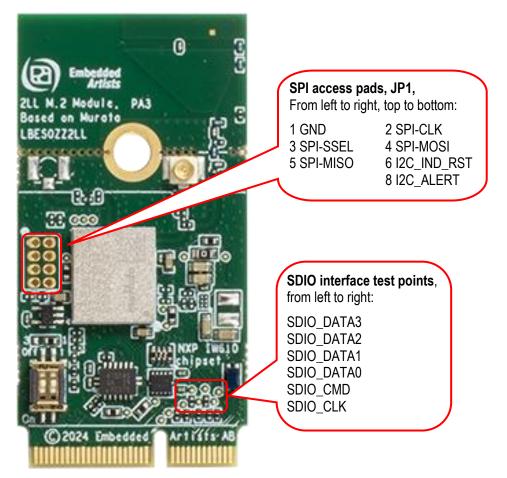

#### 3.7 IEEE802.15.4 Interface

The IW610G chipset also implements an IEEE802.15.4 interface, which is a low-rate wireless personal area network (LR-WPAN) that was developed for low-data-rate monitor and control applications and extended-life low-power-consumption uses.

The IEEE802.15.4 functionality is accessed via an SPI interface. There is no standard SPI interface defined in the M.2 standard, but there are Vendor defined and reserved pins. These are used for the SPI interface. The 2LL M.2 module has a buffer that connects/disconnects the SPI interface IW610G chipset to the M.2 pins. This buffer is only enabled if bit 0 of the on-board I2C GPIO expander is set to 1.

Besides accessing the SPI interface with the M.2 pins, the SPI signals are also available via expansion connector JP1, see table below.

| M.2 pin / name      | JP1<br>pin | SPI signal        | Direction                    | Connection                                                                                 |

|---------------------|------------|-------------------|------------------------------|--------------------------------------------------------------------------------------------|

|                     | 1          | GND               | Ground                       | Ground                                                                                     |

| 42 / VENDOR DEFINED | 2          | SPI_CLK /<br>CLK  | Input to M.2<br>Input to JP1 | SPI_SCK, the SPI clock signal<br>(from host to M.2) for the<br>IEEE802.15.4/SPI interface. |

| 64 / RESERVED       | 3          | SPI_FRM /<br>SSEL | Input to M.2<br>Input to JP1 | SPI_SSEL, SPI select signal for the IEEE802.15.4/SPI interface.                            |

| 38 / VENDOR DEFINED | 4          | SPI_RXD /<br>MOSI | Input to M.2<br>Input to JP1 | SPI_MOSI, the SPI data signal<br>(from host to M.2) for the<br>IEEE802.15.4/SPI interface. |

| 40 / VENDOR DEFINED | 5          | SPI_TXD /         | Output from                  | SPI_MISO, the SPI data signal                                                              |

|             |   | MISO | M.2<br>Output from<br>JP1 | (from M.2 to host) for the IEEE802.15.4/SPI interface.                                                                                                                                                                                                                                                            |

|-------------|---|------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 6 |      | Input to JP1              | Independent reset signal for<br>IEEE802.15.4 (from the I2C<br>GPIO expander)                                                                                                                                                                                                                                      |

|             |   |      |                           | Connects to 2LL module, signal GPIO_11, pin 38                                                                                                                                                                                                                                                                    |

|             |   |      |                           | Note that the signal is connected<br>to bit 1 of the on-board I2C GPIO<br>expander. This pin must not be<br>driven actively by the I2C GPIO<br>expander. After reset/power<br>cycle, all pins are high<br>impedance, so it should not be a<br>problem unless the I2C GPIO<br>expanders registers are<br>accessed. |

| 62 / ALERT# | 8 | INT  | Output from<br>M.2        | SPI_INT, the SPI interrupt signal (from M.2 to host) for the                                                                                                                                                                                                                                                      |

|             |   |      | Output from<br>JP1        | IEEE802.15.4/SPI interface.                                                                                                                                                                                                                                                                                       |

### 3.8 SDIO Interface

The SDIO interface conforms to the SDIO v3.0 specification, including the UHS-I modes, and is backward compatible with SDIO v2.0.

| SDIO bus speed<br>modes | Max SDIO clock<br>frequency | Max bus speed | Signaling voltage<br>according to M.2<br>specification |

|-------------------------|-----------------------------|---------------|--------------------------------------------------------|

| DS (Default speed)      | 25 MHz                      | 12.5 MByte/s  | 1.8 V                                                  |

| HS (High speed)         | 50 MHz                      | 25 MByte/s    | 1.8 V                                                  |

| SDR12                   | 25 MHz                      | 12.5 MByte/s  | 1.8 V                                                  |

| SDR25                   | 50 MHz                      | 25 MByte/s    | 1.8 V                                                  |

| SDR50                   | 100 MHz                     | 50 MByte/s    | 1.8 V                                                  |

| SDR104                  | 208 MHz                     | 100 MByte/s   | 1.8 V                                                  |

| DDR50                   | 50 MHz                      | 50 MByte/s    | 1.8 V                                                  |

#### 3.9 Wi-Fi / Bluetooth Interface Control

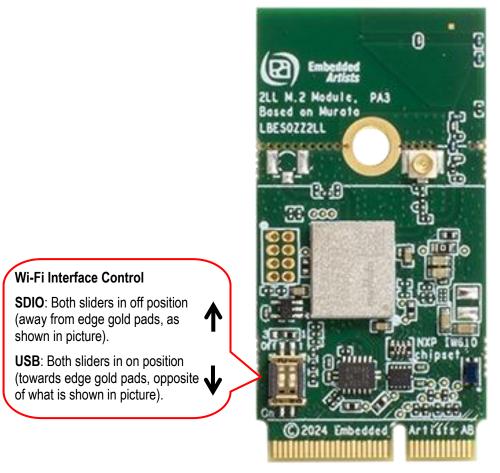

There are interface configuration pins on the IW610G chipset that control the interfaces to the different radio interfaces. With the help of two slider switches, it is possible to control these interfaces. Note that a power cycle is needed for changes to take effect.

The table below illustrates the two interface options, and the picture below illustrates the position of the slider switches.

| Slider position                                             | Wi-Fi<br>interface | Bluetooth<br>interface | IEEE802.15.4<br>interface |

|-------------------------------------------------------------|--------------------|------------------------|---------------------------|

| Both switches on OFF position (away from edge gold fingers) | SDIO               | UART                   | SPI                       |

| Both switches on ON position (towards edge gold fingers)    | USB                | USB                    | SPI                       |

Figure 5 – 2LL M.2 Module Wi-Fi Interface Control

#### 3.10 Test Points and Expansion Header

There are some test points that can be of interest to probe for SDIO debugging purposes, as illustrated in the picture below. Expansion connector, JP1, allows access to the SPI bus in case the M.2 interface does not support the (non-standard) SPI interface.

Figure 6 – 2LL M.2 Module Test Points

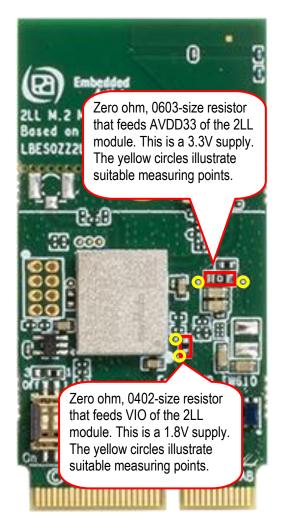

It is possible to measure the currents of the power supplies to the 2LL module, AVDD33, VIO and SD\_VIO. AVDD33 is the 3.3V that is supplied directly from the M.2 interface and VIO and SD\_VIO is an on-board 1.8V supply, generated from the supplied 3.3V via a linear regulator). If the external supply voltage (3.3V) to the M.2 module is measured it will be the sum of the AVDD33, VIO and SD\_VIO currents. The pictures below illustrate where it is possible to measure the currents.

Note that zero-ohm resistors are mounted by default. Select a series resistor with as low resistance as possible to keep the voltage drop to a minimum. Keep the drop below 100mV. AVDD33 can be about 1000-500 milli ampere in peak which means that maximum series resistance is 100 milliOhm for the AVDD33 resistor. The maximum VIO and SD\_VIO current is much lower, typically below 50mA. A suitable range for a resistor for this current is 1-2 ohm.

Figure 7 - Current Measurement

# 4 Antenna

This chapter addresses the antenna side of the module. There is an on-board, reference certified pcb trace antenna. This can be used for testing/evaluation purposes, but also for the final product. Also, for testing and evaluation purposes, it is possible to disconnect the on-board antenna and instead use the u.fl. connectors to connect external antennas.

#### 4.1 Reference Certified External Antenna

There are two reference certified antennas to choose from, see table below.

| Antenna<br>type | Supplier | Antenna Part<br>Number | Frequency<br>(MHz) | Peak Antenna<br>Gain (dBi) |

|-----------------|----------|------------------------|--------------------|----------------------------|

| Monopole        | Murata   | On-board               | 5925-7125          | 2.5                        |

| Dipole          | Unictron | WT32D1-KX              | 5925-7125          | 4                          |

Unictron H2B1WD1A3B0200 is a balanced, dipole-type, high efficiency antenna. It is ground plane independent, tripple band antenna that supports the 2400-2485MHz, 5150-5850MHz and 5925-7125 MHz frequency bands. The physical size is  $32 \times 13 \times 1.5$ mm. The antenna cable is 119 ±5 mm and the connector is MHF-I, which is a U.FL compatible connector.

Unictron H2B1WD1A3B0200 Wi-Fi 6 & 6E antenna is also referenced to as WT32D1-KX 001.

Figure 8 – Reference Certified Antenna

Note that no external antenna is included when ordering the evaluation bundle of the 2LL M.2 board.

#### 4.2 Antenna Connector

The M.2 standard specifies a 1.5 mm outer ring diameter male connector, which is compatible with the Murata MSC and IPEX MHF4 connector specifications. This connector is not used since our M.2 modules also target industrial users, where the Hirose U.FL. connector standard is more commonly used. U.FL. is compatible with the IPEX MHF1 connector specification.

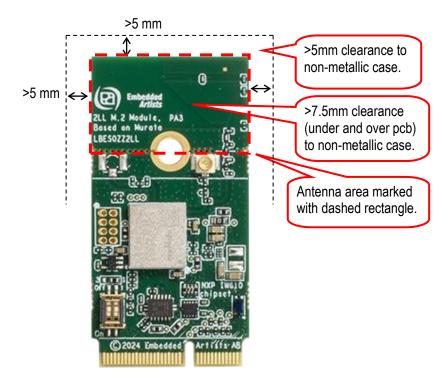

#### 4.3 Mounting and Clearance for On-board Antenna

Ideally, arrange the M.2 module so that the antenna is located at a corner of the product. Keep plastic case (i.e., non-metallic) away from the antenna area with at least 5 mm clearance (in all directions). Also keep any metal elements (e.g., connectors, battery, etc.) away from the antenna area with at least 5 mm clearance (in all directions). Keep a clearance area under and above the antenna area of at least 7.5mm, both under and over the PCB.

Human hands or body parts should be kept away (in normal use case) from the antenna area.

The ground hole in the middle shall be grounded. Use a metal stand-off according to M.2 standard (height suitable for selected M.2 connector) and use metal screw to create a proper ground connection.

Figure 9 – M.2 Module Clearance Area

#### 4.4 Overriding on-board PCB Trace Antenna

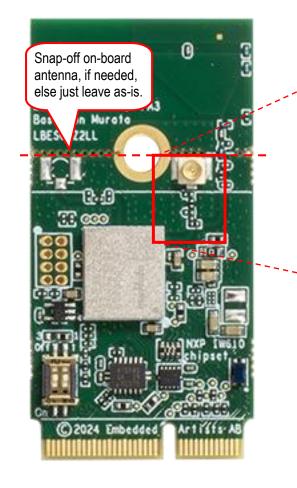

Per default, the on-board PCB trace antenna is used. The antenna connection from the 2LL module can be redirected to the U.FL. connector by just moving one zero ohm 0201 series resistor, see illustration below. The on-board trace antenna can be left as-is, or the antenna part can be snapped-off.

Figure 10 - Rework to Connect U.FL. Connector

For external antenna via U.FL. connector: Mount a 0 ohm 0201size resistor in the green rectangle.

For external antenna via U.FL. connector: Remove the 0 ohm 0201-size resistor in the red rectangle.

### 4.5 On-board PCB Trace Antenna Performance

The on-board pcb trace antenna type is monopole, certified by Murata.

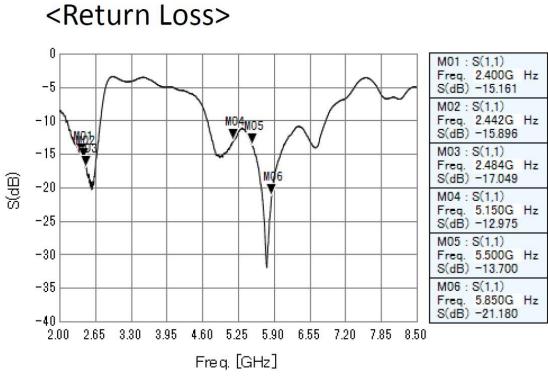

The table below lists total efficiency:

| Measurement condition      |      |      | Frequen | icy MHz | -    | ciency in<br>B | Total Efficiency in<br>% |                          |                          |                          |

|----------------------------|------|------|---------|---------|------|----------------|--------------------------|--------------------------|--------------------------|--------------------------|

|                            | 2400 | 2442 | 2484    | 5150    | 5500 | 5850           | Average<br>2 GHz<br>band | Average<br>5 GHz<br>band | Average<br>2 GHz<br>band | Average<br>5 GHz<br>band |

| Certified trace<br>antenna | -1.0 | -1.0 | -0.9    | -1.3    | -1.6 | -1.5           | -1.0                     | -1.5                     | 80.1                     | 71.5                     |

The table below lists peak gain:

| Measurement             |                                          |      | Frequer | Max dBi |                   |                   |     |      |

|-------------------------|------------------------------------------|------|---------|---------|-------------------|-------------------|-----|------|

| condition               | Frequency   2400 2442 2484   2.6 2.4 2.5 | 5150 | 5500    | 5850    | Max<br>2 GHz band | Max<br>5 GHz band |     |      |

| Certified trace antenna | 2.6                                      | 2.4  | 2.5     | 3.5     | 3.6               | 3.5               | 2.6 | 3.64 |

The pictures below illustrate the return loss and efficiency.

#### Figure 11 - Return Loss for Certified Trace Antenna

### <Efficiency>

|            |      |                      |       |      |       |      | [dBi] | [dB]       |

|------------|------|----------------------|-------|------|-------|------|-------|------------|

| LINEAR     |      | XY-                  | olane | YZ-  | olane | ZX-p | olane | Total      |

| POLARIZAT  | ION  | hor.                 | ver.  | hor. | ver.  | hor. | ver.  | Efficiency |

| 2400 MHz   | MAX. | -1.6                 | -0.9  | 2.6  | -16.3 | -2.2 | 1.0   |            |

|            | AVE. | -4.9                 | -4.6  | -2.0 | -20.4 | -8.3 | -0.9  | -1.0       |

| 2442 MHz   | MAX. | -1.6                 | -0.8  | 2.4  | -15.0 | -2.0 | 1.1   |            |

| 2442 11112 | AVE. | E5.1 -4.6 -1.9 -19.5 | -8.3  | -0.7 | -1.0  |      |       |            |

| 2484 MHz   | MAX. | -1.7                 | -0.7  | 2.5  | -13.6 | -1.7 | 1.6   |            |

|            | AVE. | -5.2                 | -4.5  | -1.6 | -18.7 | -8.2 | -0.5  | -0.9       |

|              |      |                   |      |          |                      |       | [dBi]             | [dB]       |

|--------------|------|-------------------|------|----------|----------------------|-------|-------------------|------------|

| LINEAR       |      | XY-plane YZ-plane |      | ZX-plane |                      | Total |                   |            |

| POLARIZATION |      | hor.              | ver. | hor.     | ver.                 | hor.  | ver.              | Efficiency |

| 5150 MHz     | MAX. | 2.3               | 0.1  | 2.2      | - <mark>11.4</mark>  | 3.5   | -0.2              |            |

|              | AVE. | -4.1              | -4.5 | -2.0     | -19.2                | -3.9  | -3.9              | -1.3       |

| 5500 MHz     | MAX. | 2.3               | -0.6 | 1.0      | -12.7                | 3.6   | <mark>-1.8</mark> |            |

| 3300 14112   | AVE. | -4.3              | -5.0 | -2.4     | -20.0                | -4.3  | -5.1              | -1.6       |

| 5850 MHz     | MAX. | 2.3               | -0.7 | 1.0      | -12.9                | 3.5   | -1.6              |            |

|              | AVE. | -4.1              | -5.4 | -2.4     | - <mark>1</mark> 9.8 | -4.2  | -5.5              | -1.5       |

Figure 12 – Efficiency for Certified Trace Antenna

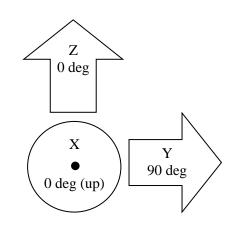

The directivity measurements are presented below for the 2 GHz and 5GHz bands with the orientation as illustrated below.

Figure 13 –Plane Orientations

# <Directivity>

@2442MHz

| х   | Y plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e [dBi]          | Y   | <b>Z</b> plar | <b>1e</b> [dBi]  | z   | X plan | e [dBi]                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|---------------|------------------|-----|--------|------------------------------|

| 270 | a contraction of the second se | 90<br>horizontal | 270 |               | 90<br>horizontal | 270 |        | 90<br>horizontal<br>vertical |

|     | HOR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VER.             |     | HOR.          | VER.             |     | HOR.   | VER.                         |

| MAX | -1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -0.8             | MAX | 2.4           | -15.0            | MAX | -2.0   | 1.1                          |

| AVE | -5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -4.6             | AVE | -1.9          | -19.5            | AVE | -8.3   | -0.7                         |

### @5500MHz

| Х   | Y plar | e [dBi]                       | Y   | Z plar | ie [dBi]                       | Z   | X plan | e [dBi]                      |

|-----|--------|-------------------------------|-----|--------|--------------------------------|-----|--------|------------------------------|

| 270 |        | 90<br>horizon tal<br>vertical | 270 |        | 90<br>hori zon tal<br>vertical | 270 |        | 90<br>horizontal<br>vertical |

|     | HOR.   | VER.                          |     | HOR.   | VER.                           |     | HOR.   | VER.                         |

| MAX | 2.3    | -0.6                          | MAX | 1.0    | -12.7                          | MAX | 3.6    | -1.8                         |

| AVE | -4.3   | -5.0                          | AVE | -2.4   | -20.0                          | AVE | -4.3   | -5.1                         |

Figure 14 – Directivity for Certified Trace Antenna

# 5 Software and Support

This chapter contains information about software and support.

#### 5.1 Software Driver

The IW610G chipset does not contain any persistent software. A firmware image must be downloaded by the host at start-up. This is the responsibility of the operating system driver.

There are three different cases, depending on which host processor is used:

1. Embedded Artists' Computer-on-Modules, (u)COM, as host processor

Embedded Artists' Linux BSPs and SDKs for the different (u)COM board contains all drivers available and pre-configured. Everything has been tested and works out-of-the-box on the different iMX Developer's Kits.

| iMX Developer's Kit    | 2LL M.2 support                          |

|------------------------|------------------------------------------|

| iMX93 uCOM             | Preliminary support in Linux BSP v6.6.23 |

| iMX8M Mini uCOM        | Preliminary support in Linux BSP v6.6.23 |

| iMX8M Nano uCOM        | No                                       |

| iMX8M COM              | No                                       |

| iMX7 Dual COM          | No                                       |

| iMX7 Dual uCOM         | No                                       |

| iMX7ULP uCOM           | No                                       |

| iMX6 Quad COM          | No                                       |

| iMX6 DualLite COM      | No                                       |

| iMX6 SoloX COM         | No                                       |

| iMX6 UltraLite/ULL COM | No                                       |

| iMX RT1176 uCOM        | No                                       |

| iMX RT1166 uCOM        | No                                       |

| iMX RT1064 uCOM        | No                                       |

| iMX RT1062 OEM         | No                                       |

#### 2. Other i.MX based, for example NXP's EVKs

Murata has created documentation how to compile the Linux kernel for the NXP EVKs https://wireless.murata.com/products/rf-modules-1/wi-fi-bluetooth-for-nxp-i-mx.html#Linux

#### 3. Non-i.MX host processor

There is no ready-to-go driver exist. Contact Murata to check driver availability on the hardware platform used.

#### 5.2 Support

Embedded Artists supports customers that use our M.2 module in combination with Embedded Artists' Computer-on-Modules, (u)COM, based on NXP's i.MX RT/8/9 families.