iMX7ULP uCOM Board - Datasheet

**Document status: Preliminary**

Copyright 2024 © Embedded Artists AB

# iMX7ULP uCOM Board, rev PB1 Datasheet

Get Up-and-Running Quickly and Start Developing Your Application On Day 1!

#### **Embedded Artists AB**

Rundelsgatan 14 211 36 Malmö Sweden

https://www.EmbeddedArtists.com

#### Copyright 2024 © Embedded Artists AB. All rights reserved.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Embedded Artists AB.

#### Disclaimer

Embedded Artists AB makes no representation or warranties with respect to the contents hereof and specifically disclaim any implied warranties or merchantability or fitness for any particular purpose. The information has been carefully checked and is believed to be accurate, however, no responsibility is assumed for inaccuracies.

Information in this publication is subject to change without notice and does not represent a commitment on the part of Embedded Artists AB.

#### Feedback

We appreciate any feedback you may have for improvements on this document.

#### Trademarks

All brand and product names mentioned herein are trademarks, services marks, registered trademarks, or registered service marks of their respective owners and should be treated as such.

# **Table of Contents**

| 1     | Document Revision History                     | 5  |

|-------|-----------------------------------------------|----|

| 2     | Introduction                                  | 6  |

| 2.1   | Hardware                                      | 6  |

| 2.2   | Software                                      | 7  |

| 2.3   | Features and Functionality                    | 7  |

| 2.4   | Reference Documents                           | 9  |

| 3     | Board Pinning                                 | 11 |

| 3.1   | Pin Numbering                                 | 11 |

| 3.2   | Pin Assignment                                | 12 |

| 4     | uCOM Adapter Board                            | 20 |

| 4.1   | Pin Numbering                                 | 20 |

| 4.2   | Pin Assignment                                | 21 |

| 5     | Pin Mapping                                   | 33 |

| 5.1   | Functional Multiplexing on I/O Pins           | 33 |

| 5.1.1 | Alternative I/O Function List                 | 33 |

| 5.2   | I/O Pin Control                               | 33 |

| 6     | Interface Description                         | 34 |

| 6.1   | EAuCOM Standard Pin and Interface Allocation  | 34 |

| 6.2   | Display Interface                             | 35 |

| 6.3   | JTAG                                          | 35 |

| 6.4   | USB                                           | 37 |

| 7     | Boot Control                                  | 38 |

| 7.1   | COM Carrier Board Boot Control Jumpers        | 40 |

| 7.2   | uCOM Adapter Board Boot Sliders               | 41 |

| 8     | Powering and PMIC Integration                 | 43 |

| 8.1   | Available Power Supply Rails                  | 43 |

| 8.2   | Integration without Battery                   | 44 |

| 8.3   | Integration with 1S LiPo Rechargeable Battery | 44 |

| 9     | Power Modes                                   | 45 |

| 10    | Murata 1LV Wi-Fi/BT Module Mounting Option    | 47 |

| 11    | Technical Specification                       | 48 |

| 11.1  | Absolute Maximum Ratings                      | 48 |

| 11.2  | Recommended Operating Conditions              | 48 |

| 11.3  | Power Ramp-Up Time Requirements               | 48 |

| 11.4   | Electrical Characteristics                             | 48 |

|--------|--------------------------------------------------------|----|

| 11.4.1 | Reset Output Voltage Range                             | 48 |

| 11.4.2 | Reset Input                                            | 48 |

| 11.5   | Power Consumption                                      | 49 |

| 11.6   | Mechanical Dimensions                                  | 49 |

| 11.6.1 | DF40C Socket                                           | 51 |

| 11.6.2 | Module Assembly Hardware                               | 51 |

| 11.7   | Environmental Specification                            | 51 |

| 11.7.1 | Operating Temperature                                  | 51 |

| 11.7.2 |                                                        | 52 |

| 11.8   | Thermal Design Considerations                          | 52 |

| 11.8.1 | Thermal Parameters                                     | 52 |

| 11.9   | Product Compliance                                     | 52 |

| 12     | Functional Verification and RMA                        | 53 |

| 13     | Things to Note                                         | 54 |

| 13.1   | Shared Pins and Multiplexing                           | 54 |

| 13.2   | Use COM Carrier Board rev E/E1, or Later               | 54 |

| 13.3   | COM Carrier Board Revision and HDMI Interface          | 54 |

| 13.4   | uCOM Adapter Board rev A/A1 and Different uCOM Modules | 54 |

| 13.5   | uCOM Adapter Board rev A/A1 and J12 Usage              | 55 |

| 13.6   | Only Use EA Board Support Package (BSP)                | 56 |

| 13.7   | OTP Fuse Programming                                   | 56 |

| 13.8   | Write Protect on Parameter Storage E2PROM              | 57 |

| 13.9   | Integration - Contact Embedded Artists                 | 57 |

| 13.10  | ESD Precaution when handling iMX7ULP uCOM Board        | 58 |

| 13.11  | EMC / ESD                                              | 58 |

| 14     | Custom Design                                          | 59 |

| 15     | Disclaimers                                            | 60 |

| 15.1   | Definition of Document Status                          | 61 |

# **1** Document Revision History

| Revision | Date       | Description                                                     |  |

|----------|------------|-----------------------------------------------------------------|--|

| PA1      | 2019-10-04 | First version.                                                  |  |

| PA2      | 2019-10-09 | Corrected measurement in Figure 10.                             |  |

| PA3      | 2019-10-15 | Added information about USB multiplexing.                       |  |

| PA4      | 2020-07-30 | Added section 13.5                                              |  |

| PA5      | 2024-05-02 | The document has been updated to reflect rev PB1 of the design. |  |

### 2 Introduction

This document is a datasheet that specifies and describes the *iMX7ULP uCOM Board* mainly from a hardware point of view. Some basic software related issues are also addressed, like booting and functional verification, but there are separate software development manuals that should also be consulted.

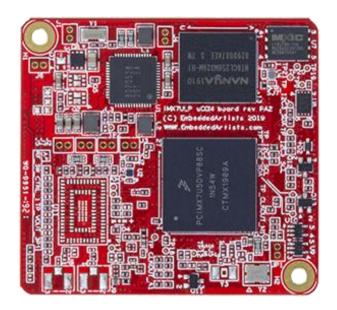

#### 2.1 Hardware

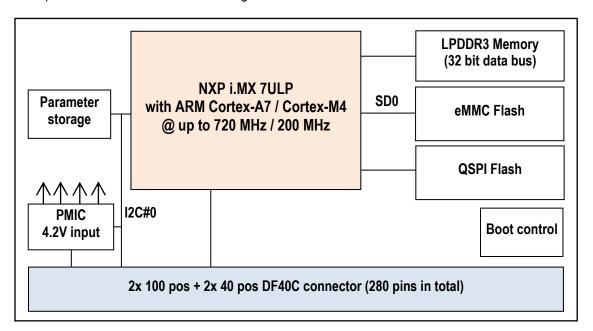

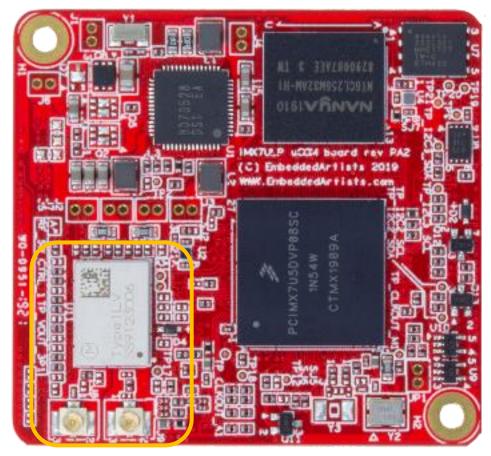

The *iMX7ULP uCOM Board* is a Computer-on-Module (COM) based on NXP's ARM Cortex-A7 / M4 i.MX 7ULP System-on-Chip (SoC) application processor. The board provides a quick and easy solution for implementing a high-performance ARM Cortex-A7 / M4 based design. The Cortex-A7 core runs at up to 720MHz (650MHz for industrial version) and the Cortex-M4 core at up to 200 MHz.

The heterogeneous core architecture enables the system to run an OS like Linux on the Cortex-A7 core and a Real-Time OS (RTOS) on the Cortex-M4. This architecture is ideal for real time applications where Linux cannot be used for all time critical tasks. The Cortex-M4 can handle (real time) critical tasks and can also be used to lower the power consumption.

The *iMX7ULP uCOM Board* delivers high computational and graphical performance at low power consumption. The on-board PMIC together with a LPDDR3 memory sub-system reduce the power consumption.

The SoC is part of the scalable i.MX 6/7/8/9 product family. There is a range of i.MX 6/7/8/9 (u)COM Boards from Embedded Artists with single, dual and quad Cortex-A cores, with or without a heterogeneous Cortex-M core. Groups of boards (uCOM and COM) share the same basic pinning for maximum flexibility and performance scalability.

The *iMX7ULP uCOM Board* has an ultra-small form factor and shields the user from a lot of complexity of designing a high performance system. It is a robust and proven design that allows the user to focus the product development, shorten time to market and minimize the development risk.

The *iMX7ULP uCOM Board* targets a wide range of applications, such as:

- Portable systems

- HMI/GUI solutions

- Portable medical and health care

- Connected vending machines

- Point-of-Sale (POS) applications

- Access control panels

- Audio

- IP phones

- Smart appliances

- Wearables

- Home energy management systems

- Industrial automation

- HVAC Building and Control Systems

- Smart Grid and Smart Metering

- Smart Toll Systems

- Data acquisition

- Communication gateway solutions

- Connected real-time systems

- ...and much more

The picture below illustrates the block diagram of the *iMX7ULP uCOM Board*.

The *iMX7ULP uCOM Board* pin assignment focus on direct connection to (carrier board) interface connectors and minimize trace and layer crossing. This is important for high speed, serial interfaces with impedance controlled differential pairs. As a result, carrier boards can be designed with few routing layers. In many cases, a four layer PCB is enough to implement advanced and compact carrier boards. The pin assignment is common for the *iMX RT/7/8/9 uCOM Boards* from Embedded Artists and the general, so called, EAuCOM specification is found in separate document.

#### 2.2 Software

The *iMX7ULP uCOM Board* has a Board Support Package (BSP) for Linux and an SDK for the Cortex-M4 side. Precompiled images are available. Embedded Artists work with partners that can provide support for other operating systems (OS). For more information contact Embedded Artists support.

This document has a hardware focus and does not cover software development. See other documents related to the *iMX7ULP uCOM Board* for more information about software development.

#### 2.3 Features and Functionality

The i.MX 7ULP is a powerful SoC. The full specification can be found in NXP's *i.MX 7ULP Datasheet* and *i.MX 7ULP Reference Manual*. The table below lists the main features and functions of the *iMX7ULP uCOM board* - which represents Embedded Artists integration of the i.MX 7ULP SoC. Due to pin configuration some functions and interfaces of the i.MX 7ULP many not be available at the same time. See i.MX 7ULP SoC datasheet and reference manual for details. Also see pin multiplexing Excel sheet for details.

| Group | Feature       |                                               | iMX7ULP uCOM Board                                         |

|-------|---------------|-----------------------------------------------|------------------------------------------------------------|

| CPUs  | NXP SoC       | commercial temp. range industrial temp. range | MCIMX7U5DVP07S (0 - 70° C)<br>MCIMX7U5CVP06S (-40 - 85° C) |

|       | CPU Cores     |                                               | 1x Cortex-A7<br>1x Cortex-M4F with MPU/FPU                 |

|       | L1 Instructio | n cache                                       | 32 KByte on Cortex-A7<br>8 KByte on Cortex-M4              |

|                              | L1 Data cache                                      | 32 KByte on Cortex-A7                                                                                                 |

|------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|                              |                                                    | 8 KByte on Cortex-M4                                                                                                  |

|                              | L2 Cache on Cortex-A7 core                         | 256 KByte                                                                                                             |

|                              | On-chip SRAM                                       | 256 KByte                                                                                                             |

|                              | NEON SIMD media accelerator on Cortex-A7           | $\checkmark$                                                                                                          |

|                              | Maximum CPU frequency                              | 650/720 MHz on Cortex-A7 in<br>overdrive mode<br>500 MHz max on Cortex-A7 in<br>standard mode<br>200 MHz on Cortex-M4 |

| Security                     | High Assurance Boot                                | $\checkmark$                                                                                                          |

| Functions                    | Cryptographic Acceleration and Assurance<br>Module | $\checkmark$                                                                                                          |

|                              | Secure Non-Volatile Storage                        | $\checkmark$                                                                                                          |

|                              | System JTAG controller                             | $\checkmark$                                                                                                          |

|                              | Extended Resource Domain Controller (XRDC)         | $\checkmark$                                                                                                          |

| Memory                       | LPDDR3 RAM Size                                    | 1 GByte, default. Other on request.                                                                                   |

|                              | LPDDR3 RAM Speed                                   | 720 MT/s                                                                                                              |

|                              | LPDDR3 RAM Memory Width                            | 32 bit                                                                                                                |

|                              | eMMC NAND Flash (8 bit)                            | 8 GByte, default. Other on request.                                                                                   |

|                              | QSPI                                               | 4 MByte, default. Other on request.                                                                                   |

| Graphical<br>Processing      | Multimedia Graphics Processing Unit (GPU)          | OpenGL ES2.0/1.1, Desktop<br>OpenGL 2.1, OpenVG1.1                                                                    |

| Graphical<br>Output          | MIPI-DSI, 2 lanes                                  | ✓                                                                                                                     |

| Graphical<br>Input           | Parallel Camera Sensor Interface                   | $\checkmark$                                                                                                          |

| Analog I/O                   | 2x ADC, 12-bit                                     | $\checkmark$                                                                                                          |

|                              | 2x DAC, 12-bit                                     | $\checkmark$                                                                                                          |

|                              | 2x Comparators                                     | $\checkmark$                                                                                                          |

| Connectivity                 | USB2.0 OTG port with Phy                           | $\checkmark$                                                                                                          |

| Interfaces<br>(all functions | HSIC USB                                           | $\checkmark$                                                                                                          |

| are not<br>available at      | 2x I2S                                             | $\checkmark$                                                                                                          |

| the same time)               | 1x SD3.0/MMC 5.0                                   | <ul> <li>✓ SD0 interface used on-board to<br/>eMMC</li> </ul>                                                         |

|                              | 2x SPI, 4x UART, 4x I <sup>2</sup> C               | $\checkmark$                                                                                                          |

|                              | PWMs, FlexIOs, WDOG                                | $\checkmark$                                                                                                          |

| Other                        | PMIC (MC34PF1550A4)                                | $\checkmark$                                                                                                          |

| E2PROM storing board information | $\checkmark$ |

|----------------------------------|--------------|

| On-board RTC via CPU             | $\checkmark$ |

| On-board watchdog functionality  | $\checkmark$ |

#### 2.4 Reference Documents

The following documents are important reference documents and should be consulted when integrating the *iMX7ULP uCOM board*:

- EACOM Board Specification

- EACOM Board Integration Manual

The following NXP documents are also important reference documents and should be consulted for functional details:

- IMX7ULPCEC, i.MX 7ULP Applications Processors Consumer Products Data Sheet, latest revision

- IMX7ULPIEC, i.MX 7ULP Applications Processors Industrial Products Data Sheet, latest revision

- IMX7ULPRM, i.MX 7ULP Applications Processors Reference Manual, latest revision

- IMX7ULPSRM, Security Reference Manual for i.MX 7ULP, latest revision

- IMX7ULPCE, Chip Errata for the i.MX 7ULP, latest revision

Note: It is the user's responsibility to make sure all errata published by the manufacturer are taken note of. The manufacturer's advice should be followed.

- AN12573, i.MX 7ULP Power Consumption Measurement, latest revision

- i.MX 7ULP Product Lifetime Usage, latest revision

The following documents are external industry standard reference documents and should also be consulted when applicable:

- eMMC (Embedded Multi-Media Card) the eMMC electrical standard is defined by JEDEC JESD84-B45 and the mechanical standard by JESD84-C44 (www.jedec.org)

- The I2C Specification, Version 2.1, January 2000, Philips Semiconductor (now NXP) (www.nxp.com)

- I2S Bus Specification, Feb. 1986 and Revised June 5, 1996, Philips Semiconductor (now NXP) (www.nxp.com)

- JTAG (Joint Test Action Group) defined by IEEE 1149.1-2001 IEEE Standard Test Access Port and Boundary Scan Architecture (www.ieee.org)

- MXM3 Graphics Module Mobile PCI Express Module Electromechanical Specification, Version 3.0, Revision 1.1, © 2009 NVIDIA Corporation (www.mxm-sig.org)

- SD Specifications Part 1 Physical Layer Simplified Specification, Version 3.01, May 18, 2010,

© 2010 SD Group and SD Card Association (Secure Digital) (www.sdcard.org)

- SPI Bus "Serial Peripheral Interface" de-facto serial interface standard defined by Motorola. A good description may be found on Wikipedia (http://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface\_Bus)

- DSI (Display Serial Interface) The DSI standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Alliance") (www.mipi.org)

- USB Specifications (www.usb.org)

# **3 Board Pinning**

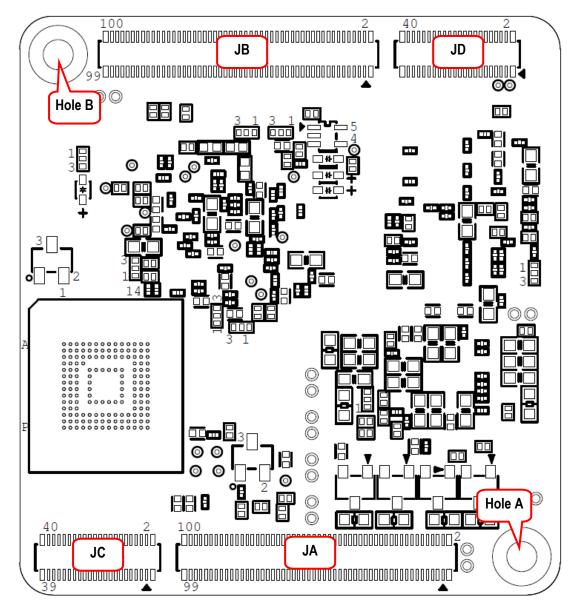

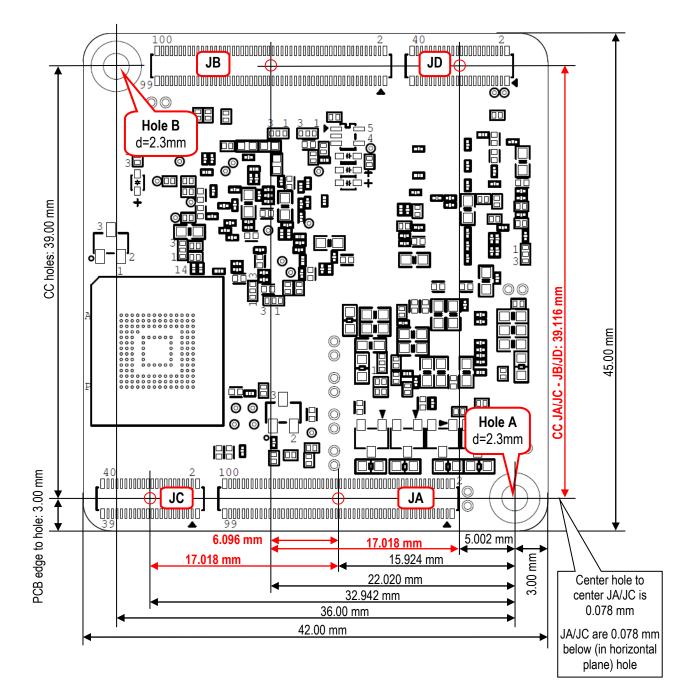

Embedded Artists has defined the EAuCOM board standard with 42 x 45 mm boards that use Hirose DF40C connectors. Note that this is not the same as the EACOM board standard with module size 82 x 50 mm. Chapter 4 describes an adapter board that converts an EAuCOM board into an EACOM board. This way, the same carrier board can be used for all iMX Developer's Kits. See the *EAuCOM Board specification* document for details and background information. Hereafter this standard will be referred to as **EAuCOM**.

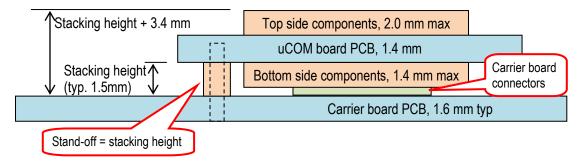

There are four Hirose DF40C expansion connectors; two 100 pos and two 40 pos connectors. The 0.4mm pitch connectors have a board-to-board stacking height of only 1.5mm. There are also versions of the receptacle connectors that give 3.0mm stacking height.

#### 3.1 Pin Numbering

The figure below illustrates the location of the four expansion connectors and their respective pin numbering on the bottom side of the *iMX7ULP uCOM Board*.

Figure 2 - iMX7ULP uCOM (EAuCOM standard) Board Pin Numbering, Bottom Side

#### 3.2 Pin Assignment

This section describes the pin assignment of the board, with the following columns:

| Connector and Pin number | The pin numbers are listed in consecutive order. Odd pin numbers are on one row and even numbers on the other row.                                                                              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-i.MX 7ULP signals    | Lists signals that are not directly connected to the i.MX 7ULP SoC.<br>These signals are typically related to powering and connected to the<br>on-board Power Management IC (PMIC), BD70528MWV. |

| i.MX 7ULP Ball Name      | The name of the ball of the i.MX 7ULP SoC that is connected to this pin.                                                                                                                        |

| Alternative Pin Function | Information if the signal is a dedicated interface or a general pin that can multiples different signals. See separate Excel sheet for details about available multiplexing alternatives.       |

| Notes                    | When relevant, the preferred pin function is listed.                                                                                                                                            |

Note that some pins are EAuCOM board *type specific*, meaning that these pins might not be compatible with other EAuCOM boards. Using these may result in lost compatibility between EAuCOM boards, but not always. Check details between EAuCOM boards of interest.

The table below lists the pins on expansion connector JA (100-pos connector).

| JA<br>Pin Number          | EAuCOM Board<br>Signal | i.MX 7ULP Ball<br>Name | Alternative<br>Pin Function? | Notes                                                                                                                |

|---------------------------|------------------------|------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 1-8                       | VIN_VBAT               | PMIC: VBAT             |                              | System supply voltage, see chapter 8 for more details.                                                               |

| 9-16                      | GND                    |                        |                              |                                                                                                                      |

| 17                        | SNVS                   | PMIC: SNVS             |                              | Voltage rail, see chapter 8 for more details.                                                                        |

|                           |                        |                        |                              | Connected to pin 30 (VSNVS) of PMIC (MC34PF1550A4)                                                                   |

| 18                        | VDD_RTC                |                        |                              | Not connected. On-board RTC powered via VIN.                                                                         |

|                           |                        |                        |                              | Connected to pin 31 (LICELL) of PMIC (MC34PF1550A4)                                                                  |

| 19, 21, 23,<br>25, 27, 29 | VDD_1V8                | PMIC: BUCK3            |                              | 1.8V voltage rail, see chapter 8 for more details.                                                                   |

| 20, 22, 24,<br>26, 28, 30 | VDD_3V3                | PMIC: VLDO1            |                              | 3.3V voltage rail, see chapter 8 for more details.                                                                   |

| 31-32                     | GND                    |                        |                              |                                                                                                                      |

| 33                        | Board specific         | DAC0_OUT               | No                           |                                                                                                                      |

| 34, 36, 38,<br>40, 42     | VDD_RF                 |                        |                              | Not connected per default. Can optionally power on-board RF-module. Requires special order for this mounting option. |

| 35                        | Board specific         | DAC1_OUT               | No                           |                                                                                                                      |

| 37                        | Board specific         | PTF14                  | Yes                          |                                                                                                                      |

| 39                        | Board specific         | PTF4                   | Yes                          |                                                                                                                      |

| 41                        | GND                    |                        |                              |                                                                                                                      |

| 43                        | Board specific         | PTF5                   | Yes                          |                                                                                                                      |

| 44                        | GND                    |                        |                              |                                                                                                                      |

| 45                        | Board specific         | PTF6                   | Yes                          |                                                                                                                      |

| 46                        | GND                    |                        |                              |                                                                                                                      |

| 47                        | Board specific         | PTF7                   | Yes                          |                                                                                                                      |

| 48                        | VBAT_TEMP              | PMIC: NTC              |                              | Battery temperature, see chapter 8 for more details.                                                                 |

| 49                | Board specific | PTF8     |     |                                                                                                                                                                                                          |

|-------------------|----------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50                | VBAT_CURRP     | -        |     | Not connected                                                                                                                                                                                            |

| 51                | GND            |          |     |                                                                                                                                                                                                          |

| 52                | VBAT_CURRN     | -        |     | Not connected                                                                                                                                                                                            |

| 53                | Board specific | PTF9     | Yes |                                                                                                                                                                                                          |

| 54, 56, 58,<br>60 | PSU_5V         | PMIC     |     | Charge voltage supply, see chapter 8 for more details.                                                                                                                                                   |

| 55                | Board specific | PTF10    | Yes |                                                                                                                                                                                                          |

| 57                | Board specific | PTF11    | Yes |                                                                                                                                                                                                          |

| 59                | Board specific | PTF15    | Yes |                                                                                                                                                                                                          |

| 61                | GND            |          |     |                                                                                                                                                                                                          |

| 62, 64, 66,<br>68 | VBUS_USB       | PMIC     |     | Charge voltage supply, see chapter 8 for more details.                                                                                                                                                   |

| 63                | Board specific | PTF0     | Yes |                                                                                                                                                                                                          |

| 65                | Board specific | PTA14    | Yes |                                                                                                                                                                                                          |

| 67                | Board specific | PTA12    | Yes |                                                                                                                                                                                                          |

| 69                | Board specific | PTA13    | Yes |                                                                                                                                                                                                          |

| 70-71             | GND            |          |     |                                                                                                                                                                                                          |

| 72                | Board specific | TAMPER   | No  |                                                                                                                                                                                                          |

| 73                | Board specific | PTA15    | Yes |                                                                                                                                                                                                          |

| 74                | Board specific | A7_POR_B |     | Connects to RESET1_B on the i.MX 7ULP SoC (ball K1).<br>The signal shall normally be left unconnected. A7 reset is<br>normally controlled from the M4.<br><b>Note</b> . This signal is 1.8V logic level. |

| 75                | Board specific | PTF1     | Yes |                                                                                                                                                                                                          |

| 76                | Board specific | -        |     | Note connected                                                                                                                                                                                           |

| 77                | Board specific | PTF2     | Yes |                                                                                                                                                                                                          |

| 78                | Board specific | -        |     | Not connected                                                                                                                                                                                            |

| 79                | Board specific | PTF3     | Yes |                                                                                                                                                                                                          |

| 80                | Board specific | -        |     | Not connected                                                                                                                                                                                            |

| 81-82             | GND            |          |     |                                                                                                                                                                                                          |

| 83                | Board specific | PTA3     | Yes |                                                                                                                                                                                                          |

| 84                | Board specific | PTC11    | Yes |                                                                                                                                                                                                          |

| 85                | Board specific | PTA4     | Yes |                                                                                                                                                                                                          |

| 86                | Board specific | PTB0     | Yes | Note. This signal is 1.8V logic level.                                                                                                                                                                   |

| 87                | Board specific | PTA6     | Yes |                                                                                                                                                                                                          |

| 88                | Board specific | PTB11    | Yes | Note. This signal is 1.8V logic level.                                                                                                                                                                   |

| 89                | Board specific | PTA5     | Yes |                                                                                                                                                                                                          |

| 90                | Board specific | PTB14    | Yes | Note. This signal is 1.8V logic level.                                                                                                                                                                   |

| 91-92             | GND            |          |     |                                                                                                                                                                                                          |

| 93                | Board specific | PTA7     | Yes |                                                                                                                                                                                                          |

| 94                | Board specific | PTF16    | Yes |                                                                                                                                                                                                          |

| 95                | Board specific | PTA1     | Yes |                                                                                                                                                                                                          |

| 96  | Board specific | PTF17 | Yes |  |

|-----|----------------|-------|-----|--|

| 97  | Board specific | PTA0  | Yes |  |

| 98  | Board specific | PTF18 | Yes |  |

| 99  | Board specific | PTA2  | Yes |  |

| 100 | Board specific | PTF19 | Yes |  |

#### The table below lists the pins on expansion connector JB (100-pos connector).

| JB<br>Pin Number | EAuCOM Board<br>Signal | i.MX 7ULP Ball<br>Name | Alternative<br>Pin Function? | Notes                                    |

|------------------|------------------------|------------------------|------------------------------|------------------------------------------|

| 1                | UART-B_RXD             | PTE11                  | Yes                          | Not connected if Wi-Fi/BT module mounted |

| 2                | GPIO-A                 | PTC8                   | Yes                          |                                          |

| 3                | UART-B_TXD             | PTE10                  | Yes                          | Not connected if Wi-Fi/BT module mounted |

| 4                | GPIO-B                 | PTC9                   | Yes                          |                                          |

| 5                | UART-A_RXD             | PTC3                   | Yes                          |                                          |

| 6                | GPIO-C                 | PTC10                  | Yes                          |                                          |

| 7                | UART-A_TXD             | PTC2                   | Yes                          |                                          |

| 8                | GPIO-D                 | PTC14                  | Yes                          |                                          |

| 9                | UART-B_CTS             | PTE9                   | Yes                          | Not connected if Wi-Fi/BT module mounted |

| 10               | GPIO-E                 | PTC15                  | Yes                          |                                          |

| 11               | UART-B_RTS             | PTE8                   | Yes                          | Not connected if Wi-Fi/BT module mounted |

| 12               | GPIO-F                 | PTA24                  | Yes                          |                                          |

| 13               | UART-C_RXD             | PTA19                  | Yes                          |                                          |

| 14               | GPIO-G                 | PTA31                  | Yes                          |                                          |

| 15               | UART-C_TXD             | PTA18                  | Yes                          |                                          |

| 16               | GPIO-H                 | PTC0                   | Yes                          |                                          |

| 17               | GND                    |                        |                              |                                          |

| 18               | GPIO-J                 | PTC1                   | Yes                          |                                          |

| 19               | SD-A_VDD               | -                      |                              | Not connected                            |

| 20               | GPIO-K                 | PTC6                   | Yes                          |                                          |

| 21               | GND                    |                        |                              |                                          |

| 22               | GPIO-L                 | PTC7                   | Yes                          |                                          |

| 23               | SD-A_CLK               | -                      |                              | Not connected                            |

| 24               | GPIO-M                 | CLK32K                 |                              |                                          |

| 25               | SD-A_CMD               | -                      |                              | Not connected                            |

| 26               | GND                    |                        |                              |                                          |

| 27               | SD-A_DATA0             | -                      |                              | Not connected                            |

| 28               | SPI-A_SCLK             | PTA17                  | Yes                          |                                          |

| 29               | SD-A_DATA1             | -                      |                              | Not connected                            |

| 30               | SPI-A_MISO             | PTA20                  | Yes                          |                                          |

| 31               | SD-A_DATA2             | -                      |                              | Not connected                            |

| 32               | SPI-A_MOSI             | PTA16                  | Yes                          |                                          |

| 33 | SD-A_DATA3  | -            |     | Not connected                                                                                                                           |

|----|-------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 34 | SPI-A_SS0   | PTA23        | Yes |                                                                                                                                         |

| 35 | GND         |              |     |                                                                                                                                         |

| 36 | GND         |              |     |                                                                                                                                         |

| 37 | SD-A_WP     | -            |     | Not connected                                                                                                                           |

| 38 | SPI-B_SCLK  | PTC18        | Yes |                                                                                                                                         |

| 39 | SD-A_NCD    | PTA11        | Yes |                                                                                                                                         |

| 40 | SPI-B_MISO  | PTC16        | Yes |                                                                                                                                         |

| 41 | SD-A_NRST   | PTA10        | Yes |                                                                                                                                         |

| 42 | SPI-B_MOSI  | PTC17        | Yes |                                                                                                                                         |

| 43 | USB-A_OC    | PTE14        | Yes |                                                                                                                                         |

| 44 | SPI-B_SS0   | PTC19        | Yes |                                                                                                                                         |

| 45 | USB-A_PWR   | PTE15        | Yes |                                                                                                                                         |

| 46 | GND         |              |     |                                                                                                                                         |

| 47 | USB-A_VBUS  | USB_OTG_VBUS |     |                                                                                                                                         |

| 48 | I2C-A_SCL   | PTC4         | No  | Note: Do not change pin function. Must be an I2C channel since the interface is used on-board.                                          |

| 49 | USB-A_DN    | USB_OTG_DN   |     |                                                                                                                                         |

| 50 | I2C-A_SDA   | PTC5         | No  | Note: Do not change pin function. Must be an I2C channel since the interface is used on-board.                                          |

| 51 | USB-A_DP    | USB_OTG_DP   |     |                                                                                                                                         |

| 52 | I2C-B_SCL   | PTF12        | Yes | This signal as a 4.7Kohm pull-up resistor to 3.3V                                                                                       |

| 53 | USB-A_ID    | PTC13        | Yes |                                                                                                                                         |

| 54 | I2C-B_SDA   | PTF13        | Yes | This signal as a 4.7Kohm pull-up resistor to 3.3V                                                                                       |

| 55 | GND         |              |     |                                                                                                                                         |

| 56 | I2C-C_SCL   | PTA8         | Yes | This signal as a 4.7Kohm pull-up resistor to 3.3V                                                                                       |

| 57 | USB-B_OC    | -            |     | Not connected                                                                                                                           |

| 58 | I2C-C_SDA   | PTA9         | Yes | This signal as a 4.7Kohm pull-up resistor to 3.3V                                                                                       |

| 59 | USB-B_PWR   | -            |     | Not connected                                                                                                                           |

| 60 | I2C-D_SCL   | PTB12        | Yes | Note. This signal is 3.3V logic level. There is an on-board<br>voltage level translator to the 1.8V logic of PTB.                       |

|    |             |              |     | This signal as a 4.7Kohm pull-up resistor to 3.3V                                                                                       |

| 61 | USB-B_VBUS  | -            |     | Not connected                                                                                                                           |

| 62 | I2C-D_SDA   | PTB13        | Yes | Note. This signal is 3.3V logic level. There is an on-board voltage level translator to the 1.8V logic of PTB.                          |

|    |             |              |     | This signal as a 4.7Kohm pull-up resistor to 3.3V                                                                                       |

| 63 | USB-B_DN    | -            |     | Not connected                                                                                                                           |

| 64 | GND         |              |     |                                                                                                                                         |

| 65 | USB-B_DP    | -            |     | Not connected                                                                                                                           |

| 66 | GND         |              |     |                                                                                                                                         |

| 67 | USB-B_ID    | -            |     | Not connected                                                                                                                           |

| 68 | PERI_PWR_EN | PTA21        | No  | Power-enable signal for external peripherals. No external<br>must drive any signal to the i.MX7ULP SoC before this<br>signal is active. |

|    |             |              |     | The signal is active high and is connected to PTA21 and the                                                                             |

|    |                |                     |     | pin is controlled by the M4 BSP software.                                                                                                                                                                    |

|----|----------------|---------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 69 | GND            |                     |     |                                                                                                                                                                                                              |

| 70 | POR_B          | POR_B               |     | Connected to RESET0_B on the i.MX 7ULP SoC. Signal shall<br>normally only be used to connect to debug interface<br>connector. Use signals RESET_IN (JB pin 74) to cause a<br>power cycle reset of the board. |

|    |                |                     |     | Note. This signal is 1.8V logic level.                                                                                                                                                                       |

| 71 | ETH_LED_10/100 | -                   |     | Not connected                                                                                                                                                                                                |

| 72 | ONOFF          | PMIC_ONOFF          |     | Connects to ONOFF on the i.MX 7ULP SoC (ball Y2).                                                                                                                                                            |

| 73 | ETH_LED_1000   | -                   |     | Not connected                                                                                                                                                                                                |

| 74 | PWRON_B        | RESET_IN            |     | A falling edge on this input will trigger a power cycle reset of<br>the board. The power cycle is triggered by (an internal)<br>negative pulse to the PWRON (pin 6) of the MC43PF1500A4<br>PMIC.             |

| 75 | ETH_LED_ACT    | -                   |     | Not connected                                                                                                                                                                                                |

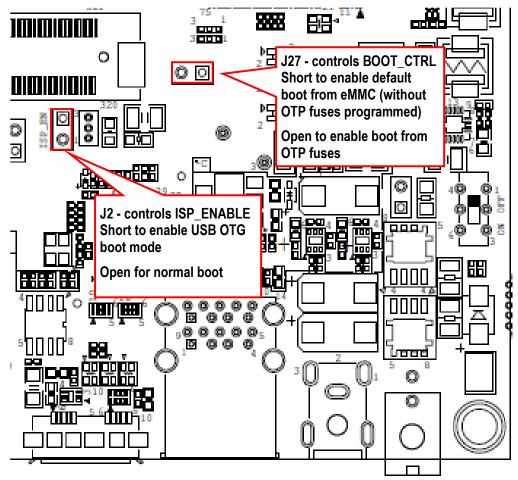

| 76 | BOOT_MODE0     | PTB4-<br>BOOT_MODE0 | Yes | This signal shall be left unconnected under normal operation.<br>The Boot Mode is controlled by signals ISP_ENABLE (JB pin<br>100) and BOOT_CTRL (JB pin 98).                                                |

|    |                |                     |     | Note. This signal is 1.8V logic level.                                                                                                                                                                       |

| 77 | GND            |                     |     |                                                                                                                                                                                                              |

| 78 | BOOT_MODE1     | PTB5-<br>BOOT_MODE1 | Yes | This signal shall be left unconnected under normal operation.<br>The Boot Mode is controlled by signals ISP_ENABLE (JB pin<br>100) and BOOT_CTRL (JB pin 98).                                                |

|    |                |                     |     | Note. This signal is 1.8V logic level.                                                                                                                                                                       |

| 79 | ETH_TRXP1      | -                   |     | Not connected                                                                                                                                                                                                |

| 80 | TEST_MODE      |                     |     |                                                                                                                                                                                                              |

| 81 | ETH_TRXN1      | -                   |     | Not connected                                                                                                                                                                                                |

| 82 | JTAG_VCC       | VDD_PTA             |     | The supply voltage of the JTAG debug interface. Is connected to the supply voltage of PTA (default is 3.3V).                                                                                                 |

| 83 | GND            |                     |     |                                                                                                                                                                                                              |

| 84 | GND            |                     |     |                                                                                                                                                                                                              |

| 85 | ETH_TRXP0      | -                   |     | Not connected                                                                                                                                                                                                |

| 86 | JTAG_TCK       | PTA29               | Yes |                                                                                                                                                                                                              |

| 87 | ETH_TRXN0      | -                   |     | Not connected                                                                                                                                                                                                |

| 88 | JTAG_TMS       | PTA26               | Yes |                                                                                                                                                                                                              |

| 89 | GND            |                     |     |                                                                                                                                                                                                              |

| 90 | JTAG_TDI       | PTA28               | Yes |                                                                                                                                                                                                              |

| 91 | ETH_TRXN3      | -                   |     | Not connected                                                                                                                                                                                                |

| 92 | JTAG_TDO       | PTA27               | Yes |                                                                                                                                                                                                              |

| 93 | ETH_TRXP3      | -                   |     | Not connected                                                                                                                                                                                                |

| 94 | JTAG_TRST      | PTA30               | Yes |                                                                                                                                                                                                              |

| 95 | GND            |                     |     |                                                                                                                                                                                                              |

| 96 | JTAG_MOD       | -                   |     | Not connected                                                                                                                                                                                                |

| 97 | ETH_TRXN2      | -                   |     | Not connected                                                                                                                                                                                                |

| 98 | BOOT_CTRL      |                     |     | Pull input low to ground to boot with default settings (controlled by on-board pullup/pulldown resistors. This is the default mode.                                                                          |

|    |                |                     |     | Leave floating/open to boot from OTP fuses (on the i.MX<br>7ULP SoC). Note that the OTP fuses must first be                                                                                                  |

|     |             | programmed, typically via UUU.                                                                                                                          |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |             | See chapter 7 for more details about boot control and options.                                                                                          |

| 99  | ETH_TRXP2 - | Not connected                                                                                                                                           |

| 100 | ISP_ENABLE  | Leave floating/open for normal boot.                                                                                                                    |

|     |             | Pull low to ground to place i.MX 7ULP SoC in USB OTG boot mode (during next power cycle). See chapter 7 for more detail about boot control and options. |

The table below lists the pins on expansion connector JC (40-pos connector). Note that this connector may not be mounted if the Murata 1LV Wi-Fi/BT module is mounted (because the signals available on this connector are all used to connect to the 1LV Wi-Fi/BT module).

| JC<br>Pin Number | EAuCOM Board<br>Signal | i.MX 7ULP Ball<br>Name | Alternative<br>Pin Function? | Notes                                                      |

|------------------|------------------------|------------------------|------------------------------|------------------------------------------------------------|

| 1                | SD-B_VCC               | VDD_PTE                |                              | Supply voltage for port E. This is a output, not an input. |

| 2                | GND                    |                        |                              |                                                            |

| 3                | SD-B_CLK               | PTE2                   | Yes                          |                                                            |

| 4                | Board specific         | -                      |                              | Not connected                                              |

| 5                | SD-B_CMD               | PTE3                   | Yes                          |                                                            |

| 6                | Board specific         | -                      |                              | Not connected                                              |

| 7                | SD-B_DATA0             | PTE1                   | Yes                          |                                                            |

| 8                | Board specific         | -                      |                              | Not connected                                              |

| 9                | SD-B_DATA1             | PTE0                   | Yes                          |                                                            |

| 10               | Board specific         | -                      |                              | Not connected                                              |

| 11               | SD-B_DATA2             | PTE5                   | Yes                          |                                                            |

| 12               | GND                    |                        |                              |                                                            |

| 13               | SD-B_DATA3             | PTE4                   | Yes                          |                                                            |

| 14               | Board specific         | -                      |                              | Not connected                                              |

| 15               | Board specific         | PTE13                  | Yes                          |                                                            |

| 16               | Board specific         | -                      |                              | Not connected                                              |

| 17               | Board specific         | PTE12                  | Yes                          |                                                            |

| 18               | Board specific         | -                      |                              | Not connected                                              |

| 19               | Board specific         | PTE7                   | Yes                          |                                                            |

| 20               | Board specific         | -                      |                              | Not connected                                              |

| 21               | Board specific         | PTC12                  | Yes                          |                                                            |

| 22               | GND                    |                        |                              |                                                            |

| 23               | Board specific         | PTE6                   | Yes                          |                                                            |

| 24               | Board specific         | -                      |                              | Not connected                                              |

| 25               | Board specific         | PTB9                   | Yes                          | Note. This signals is 1.8V logic level.                    |

| 26               | Board specific         | -                      |                              | Not connected                                              |

| 27               | SAI_TXFS               | PTB2                   | Yes                          | Note. This signals is 1.8V logic level.                    |

| 28               | Board specific         | -                      |                              | Not connected                                              |

| 29               | SAI_TXD                | РТВ3                   | Yes                          | Note. This signals is 1.8V logic level.                    |

| 30               | Board specific         | -                      |                              | Not connected                                              |

| 31               | SAI_TXC                | PTB1                   | Yes                          | Note. This signals is 1.8V logic level.                    |

| 32 | GND            |       |     |                                                                                             |

|----|----------------|-------|-----|---------------------------------------------------------------------------------------------|

| 33 | SAI_RXD        | PTB10 | Yes | Note. This signals is 1.8V logic level.                                                     |

| 34 | Board specific | -     |     | Not connected                                                                               |

| 35 | Board specific |       |     | Not connected                                                                               |

| 36 | Board specific | -     |     | Not connected                                                                               |

| 37 | Board specific | PTA22 | No  | Note: Leave signal unconnected. Is an on-board signal used for watchdog reset of the board. |

| 38 | Board specific | -     |     | Not connected                                                                               |

| 39 | Board specific | -     |     | Not connected                                                                               |

| 40 | Board specific | -     |     | Not connected                                                                               |

The table below lists the pins on expansion connector JD (40-pos connector).

| JD         | EAuCOM Board | i.MX 7ULP Ball Name | Alternative Pin | Notes         |

|------------|--------------|---------------------|-----------------|---------------|

| Pin Number | Signal       |                     | Function?       | NULES         |

| 1          | DSI_DN3      | TEST_CLK_N          | No              |               |

| 2          | CSI_CKN      | -                   |                 | Not connected |

| 3          | DSI_DP3      | TEST_CLK_P          | No              |               |

| 4          | CSI_CKP      | -                   |                 | Not connected |

| 5          | GND          |                     |                 |               |

| 6          | GND          |                     |                 |               |

| 7          | DSI_DN0      | DSI_DATA0_N         | No              |               |

| 8          | CSI_DN0      | -                   |                 | Not connected |

| 9          | SDI_DP0      | DSI_DATA0_P         | No              |               |

| 10         | CSI_DP0      | -                   |                 | Not connected |

| 11         | GND          |                     |                 |               |

| 12         | GND          |                     |                 |               |

| 13         | DSI_DN2      | -                   |                 | Not connected |

| 14         | CSI_DN1      | -                   |                 | Not connected |

| 15         | DSI_DP2      | -                   |                 | Not connected |

| 16         | CSI_DP1      | -                   |                 | Not connected |

| 17         | GND          |                     |                 |               |

| 18         | GND          |                     |                 |               |

| 19         | DSI_DN1      | DSI_DATA1_N         | No              |               |

| 20         | CSI_DN2      | -                   |                 | Not connected |

| 21         | DSI_DP1      | DSI_DATA1_P         | No              |               |

| 22         | CSI_DP2      | -                   |                 | Not connected |

| 23         | GND          |                     |                 |               |

| 24         | GND          |                     |                 |               |

| 25         | DSI_CKN      | DSI_CLK_N           | No              |               |

| 26         | CSI_DN3      | -                   |                 | Not connected |

| 27         | DSI_CKP      | DSI_CLK_P           | No              |               |

| 28         | CSI_DP3      | -                   |                 | Not connected |

| 29         | GND          |                     |                 |               |

|            |              |                     |                 |               |

Page 19

| 30 | GND            |                 |    |               |  |

|----|----------------|-----------------|----|---------------|--|

| 31 | Board specific | -               |    | Not connected |  |

| 32 | PCIE_RXN       | -               |    | Not connected |  |

| 33 | PCIE_CLKREQ_B  |                 |    | Not connected |  |

| 34 | PCIE_RXP       | -               |    | Not connected |  |

| 35 | GND            |                 |    |               |  |

| 36 | GND            |                 |    |               |  |

| 37 | PCIE_CLKN      |                 |    | Not connected |  |

| 38 | PCIE_TXN       | USB_HSIC_DATA   | No |               |  |

| 39 | PCIe_CLKP      |                 |    | Not connected |  |

| 40 | PCIE_TXP       | USB_HSIC_STROBE | No |               |  |

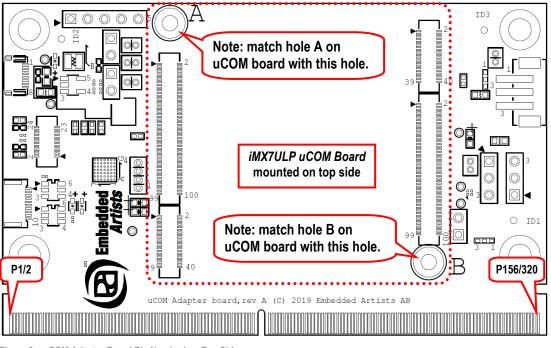

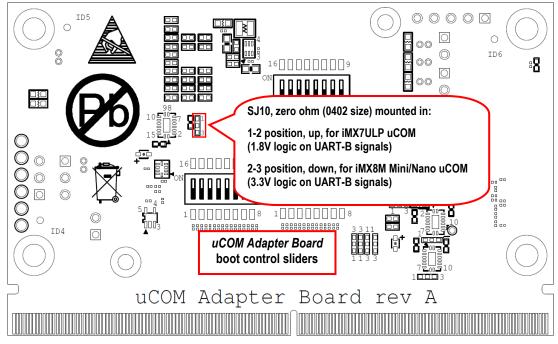

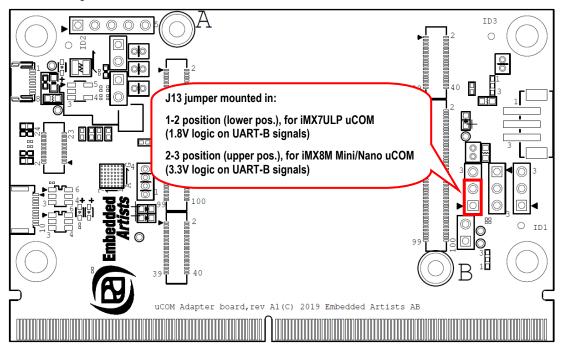

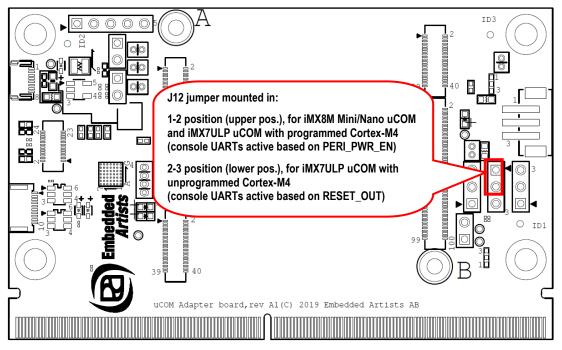

# 4 uCOM Adapter Board

Embedded Artists has defined the EACOM board standard that is based on the SMARC form factor; module size 82 x 50 mm. Note that pinning is different from the SMARC standard. See the *EACOM Board specification* document for details and background information. Hereafter this standard will be referred to as **EACOM**.

Embedded Artists has also defined the **EAuCOM** board standard with 42 x 45 mm boards that use Hirose DF40C connectors. The *uCOM Adapter Board* has been designed to convert an EAuCOM board into an EACOM board. This way, the same carrier board can be used for all *iMX Developer's Kits*.

The *iMX7ULP uCOM Developers Kit V2* consists of:

- One iMX7ULP uCOM Board, mounted on

- One uCOM Adapter Board , mounted on

- One COM Carrier Board V2

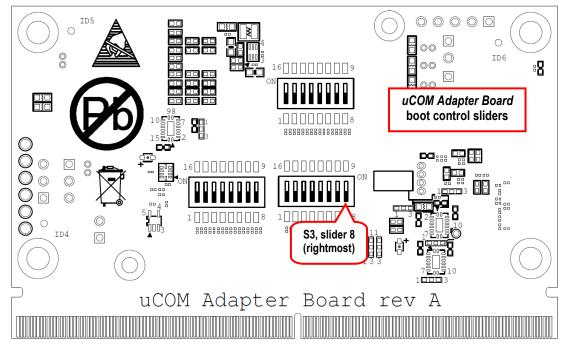

The uCOM Adapter Board contains the following functions (see schematic for details):

- MIPI-DSI to HDMI bridge

- MIPI-DSI interface directly to LCD, including backlight LED driver and touch interface

- Boot control

- Battery connector

- JTAG connector

- Optional 3.6V RF supply voltage for uCOM boards with on-board Wi-Fi/BT module

- · Possibility to measure input and output currents on supply nets

- Voltage level translation on some signals

- USB multiplexor (for iMX7ULP, which only have one USB interface)

The carrier board connector has 314 pins with 0.5 mm pitch and the *uCOM Adapter Board* is inserted in a right angle (R/A) style. The connector is originally defined for use with MXM3 graphics cards. There are multiple sources for carrier board (MXM3) connectors due to the popular standard. The signal integrity is excellent and suitable for data rates up to 5 GHz.

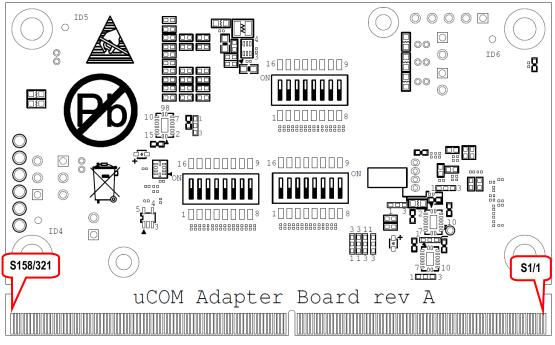

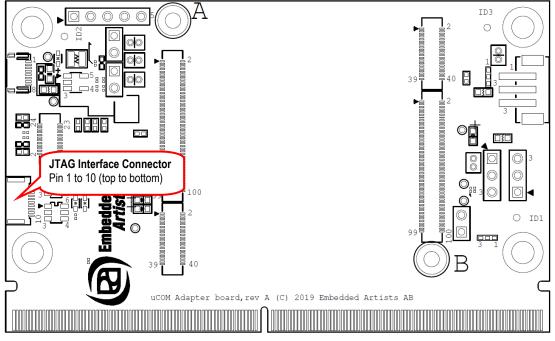

#### 4.1 Pin Numbering

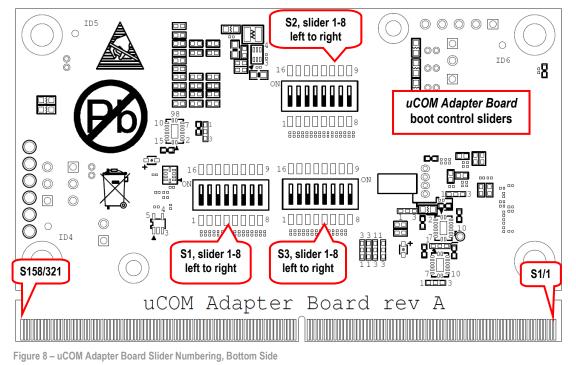

The figures below show the pin numbering for *uCOM Adapter Board*, which is compatible with EACOM boards. Top side edge fingers are numbered P1-P156. Bottom side edge fingers are numbered S1-S158. There is an alternative pin numbering that follows the MXM3 standard with even numbers on the bottom and odd numbers on the top. This numbering is from 1-321, with 7 numbers/pins (150-156) removed due to the keying.

The picture below also illustrates where the *iMX7ULP uCOM board* is mounted on the *uCOM Adapter Board*.

Figure 3 – uCOM Adapter Board Pin Numbering, Top Side

Figure 4 – uCOM Adapter Board Pin Numbering, Bottom Side

#### 4.2 Pin Assignment

This section describes the pin assignment of the board, with the following columns:

Pin number

**Px** are top side edge fingers. **Sx** are bottom side edge fingers. An alternative, consecutive, numbering is also shown with odd numbers on the top and even numbers on the bottom side.

| EACOM Board         | Describe the typical usage of the pin according to EACOM. This pin<br>usage should be followed to get compatibility between different COM<br>boards. If this is not needed, then any of the alternative functions on<br>the pin can also be used. |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i.MX 7ULP Ball Name | The name of the ball of the i.MX 7ULP SoC (or other component on the uCOM board) that is connected to this pin.                                                                                                                                   |

| Notes               | When relevant, the preferred pin function is listed.                                                                                                                                                                                              |

There are 45 ground pins, which equal to about 15%, and 10 input voltage supply pins.

Note that some pins are EACOM board *type specific*, meaning that these pins might not be compatible with other EACOM boards. Using these may result in lost compatibility between EACOM boards, but not always. Check details between EACOM boards of interest.

Note that not all EACOM-defined pins are connected on anything, typically because an interface is not supported or there are not enough free pins in the i.MX 7ULP SoC.

Further, some pins are *COM board type specific*, meaning that these pins might not be compatible with other EACOM boards. Using *type specific* pins may result in lost compatibility between EACOM boards, but not always. Check details between EACOM boards of interest.

The table below lists the top side pins, P1-P156, odd numbers.

| Top Side<br>Pin<br>Number | EAuCOM Board             | EACOM Board | i.MX 7ULP Ball<br>Name | Alternative<br>pin<br>functions? | Notes                                                                                                                                                                   |

|---------------------------|--------------------------|-------------|------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|